Instruction Classification

4-35Assembly Language Instructions

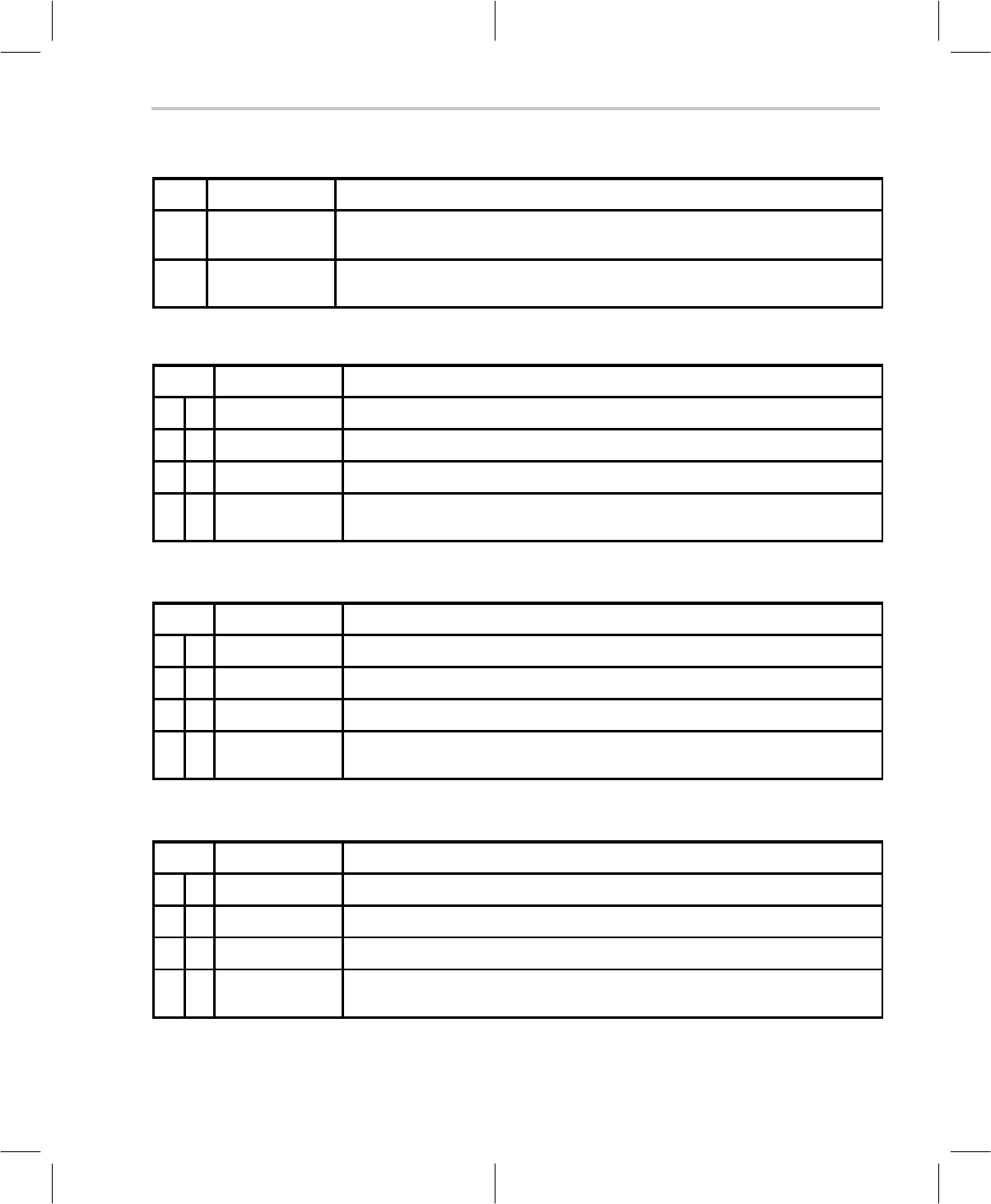

Table 4–22. Class 4a Instruction Description

C4a Mnemonic Description

0 MOV {adrs}, Rx Store Rx register to data memory referred by addressing mode {adrs}. Modify

transfer status.

1 MOV Rx, {adrs} Load Rx with the value in data memory referred by addressing mode {adrs}.

Modify transfer status.

Table 4–23. Class 4b Instruction Description

C4b Mnemonic Description

0 0 ADDB Rx, imm8 Add 8-bit positive constant to Rx register. Modify RX status.

0 1 SUBB Rx, imm8 Subtract 8-bit positive constant from Rx register. Modify RX status.

1 0 MOVB Rx, imm8 Load Rx with the an 8-bit positive constant. Modify RX status.

1 1 CMPB Rx, imm8 Store the status of the subtraction (Rx – 8-bit positive constant) into RZF and RCF

bits of the STAT register. Rx remains unchanged.

Table 4–24. Class 4c Instruction Description

C4c Mnemonic Description

0 0 ADD Rx, imm16 Add 16-bit positive constant to Rx register. Modify RX status.

0 1 SUB Rx, imm16 Subtract 16-bit positive constant from Rx register. Modify RX status.

1 0 MOV Rx, imm16 Load Rx with the an 16-bit positive constant. Modify RX status.

1 1 CMP Rx, imm16 Store the status of the subtraction (Rx – 16-bit positive constant) into RZF and RCF

bits of the STAT register. Rx remains unchanged.

Table 4–25. Class 4d Instruction Description

C4d Mnemonic Description

0 0 ADD Rx, R5 Add R5 to Rx register, Modify RX status.

0 1 SUB Rx, R5 Subtract R5 from Rx register. Modify RX status.

1 0 MOV Rx, R5 Load Rx with R5. Modify RX status.

1 1 CMP Rx, R5 Store the status of the subtraction (Rx – R5) into RZF and RCF bits of the STAT

register. Rx and R5 remain unchanged.