Interrupt Logic

2-23MSP50C6xx Architecture

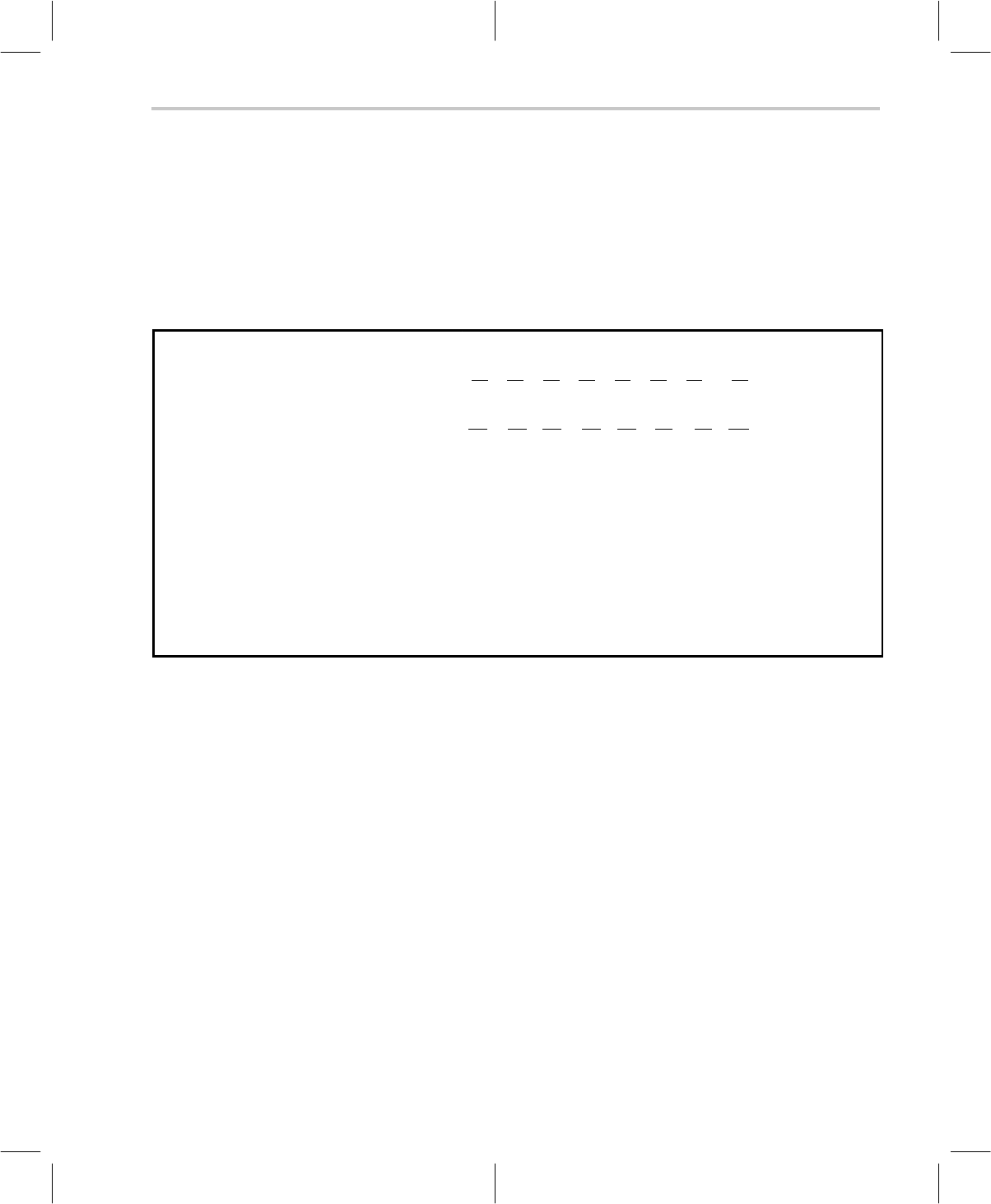

automatically SET in the interrupt flag register (IFR). The IFR is an 8-bit wide

port-addressed register; wherein, each interrupt level is represented. A set bit

in the IFR indicates that the interrupt is pending and waiting to be serviced. A

clear bit indicates that the interrupt is not currently pending. The address of the

IFR is 0x39. After a RESET low, the IFR is left in the same state it was before

the RESET low, assuming there is no interruption in power. For a full

description of the interrupt-trigger events, refer to Section 3.1.5, Internal and

External Interrupts.

(8-bit wide location)

07 06 05 04 03 02 01 00 ← INT number

IFR

Interrupt Flag register

address 0x39

D5

D4 PF D3 D2 T2 T1 DA

low high

priority priority

D5 : port D

5

falling-edge

†

PF : any port F falling-edge

D4 : port D

4

rising-edge

†

T2 : TIMER2 underflow

D3 : port D

3

falling-edge T1 : TIMER1 underflow

D2 : port D

2

rising-edge DA : DAC timer underflow

1 : A bit value 1 indicates pending interrupt waiting to be serviced.

RESET: The IFR is left in the same state it was before RESET low, assuming no interruption in power.

†

INT6 and INT7 may be associated instead with the Comparator function, if the Comparator Enable bit has been set. Refer to

Section 3.3, Comparator, for details.

Individual interrupts are enabled or disabled for service by setting or clearing

the respective bit in the interrupt mask register (IMR, 8 bits). If an interrupt level

has its bit cleared in the IMR, then the interrupt service associated with that

interrupt is disabled. Setting the bit in the IMR allows service to occur (pending

the trigger-event which is registered in the IFR).

The IMR is accessible as part of another (larger) register, namely, the

interrupt/general control register (peripheral port 0x38). After a RESET LOW,

the default value of each bit in the IMR is zero: no interrupt service enabled.

A full description of the bit locations in the interrupt/general control register can

be found in Section 3.4, Interrupt/General Control Register.

The IMR functions independently of the IFR, in the sense that interrupt-trigger

events can be registered in the IFR, even if the respective IMR bit is clear. Both

the IFR and IMR are readable and writeable as port addressed registers. To

read the register, use the IN instruction in conjunction with the port address

(0x38 or 0x39). Use the OUT instruction to write. (Refer to Section 2.6.2,

Peripheral Communications (Ports), for more information.)