I/O

3-5Peripheral Functions

and setting the EP bit enables the eight pullups. After RESET low, the default

setting for the EP bit is 0 (F-port pullups disabled).

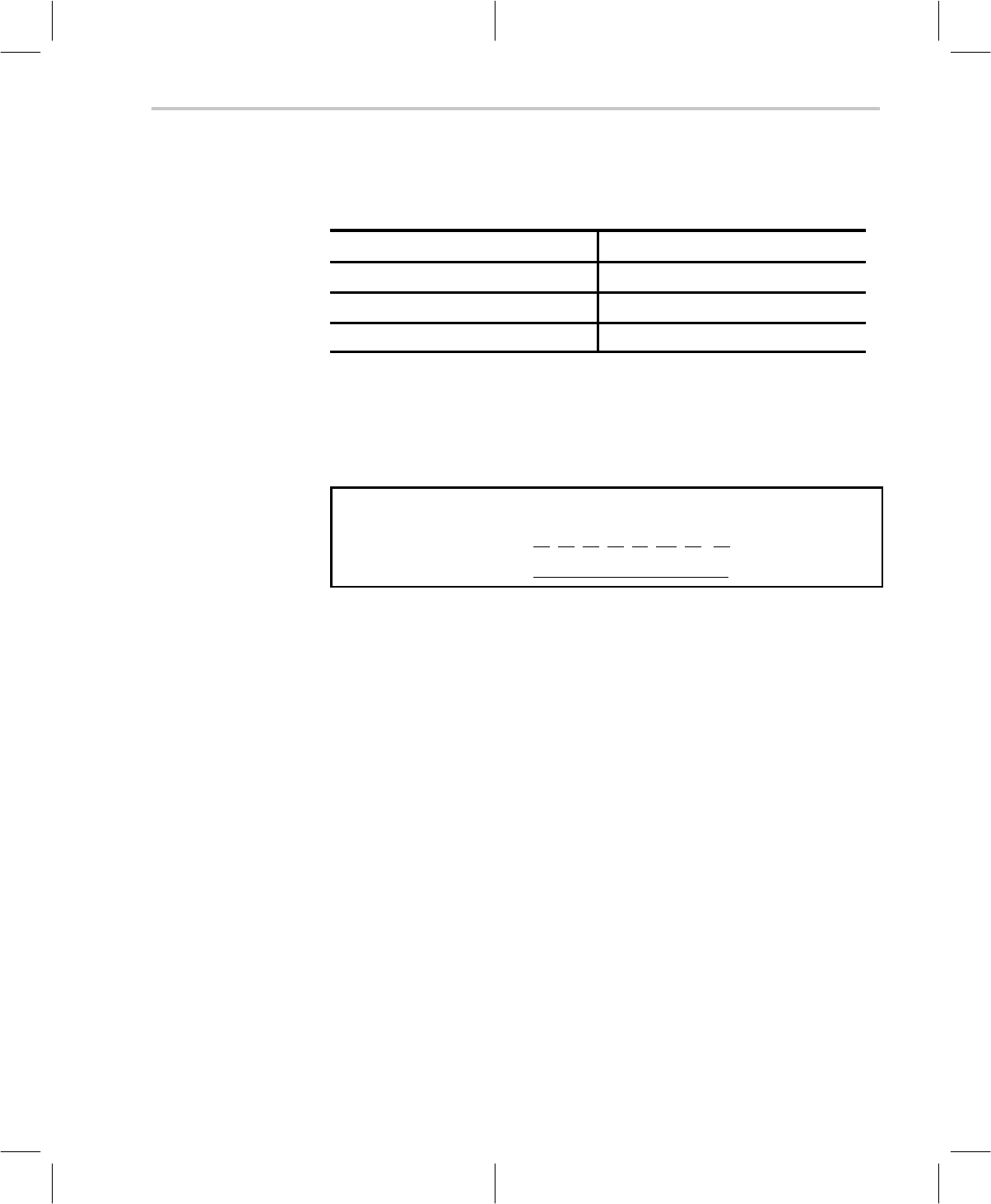

Input Port F

Data register address

0x28h

Possible input data values Low = 0 High = 1

Possible output data values N/A

Value after RESET low Pullup resistors DISABLED

When reading from the 8-bit F-port data register to a 16-bit accumulator, the

IN instruction automatically clears the extra bits in excess of 8. The desired bits

in the result will be right-justified within the accumulator.

The following table shows the bit locations of the port F address mapping:

F port Input Data register

address 0x28h

READ only

(8-bit wide location)

07

06 05 04 03 02 01 00

F7 F6 F5 F4 F3 F2 F1 F0

The external interrupt INT5 is triggered by a falling-edge event on any of the

eight port-F input pins (see Section 3.1.5, Internal and External Interrupts).

The F port input pins are gated through an eight-input AND gate, such that any

input pin going low causes the output of the AND gate to go low. Therefore,

if any input pin is held low, the device will not trigger INT5 when another input

is taken low. Specifically, INT5 is triggered if all eight port-F pins are held high,

and then one or more of these pins is taken low. This allows port F to be espe-

cially useful as a key-scan interface.

3.1.3 Dedicated Output Port G

Port G is a 16-bit wide output-only port. The output drivers have a Totem-Pole

configuration. The data driven by the output pin can be controlled by setting

or clearing the appropriate bit in the G port data register, address 0x2C. This

is done using the OUT instruction, with the 0x2C address as an argument. The

port G outputs are set to 0 (logic low) when the RESET pin is taken low. This

condition is maintained after RESET is taken high, and until the G port data

register is modified.