Interrupt/General Control Register

3-18

3.4 Interrupt/General Control Register

The interrupt/general control (IntGenCtrl) is a 16-bit wide port-mapped register

located at address 0x38. The primary component in the IntGenCtrl is the 8-bit

interrupt mask register (IMR). The IMR is used to individually enable all

interrupts except RESET. Each bit of the IMR is associated with one of the

interrupts described in Section 3.1.5. An interrupt is enabled when the

appropriate IMR bit is set. The IMR is located at bits 0 through 7 in the

IntGenCtrl. Bit 0 is associated with INT0, which is the highest priority interrupt.

Bit 7 is associated with INT7. Refer to Section 2.7, Interrupt Logic, for more

information regarding the interrupt-system logic and initialization sequence.

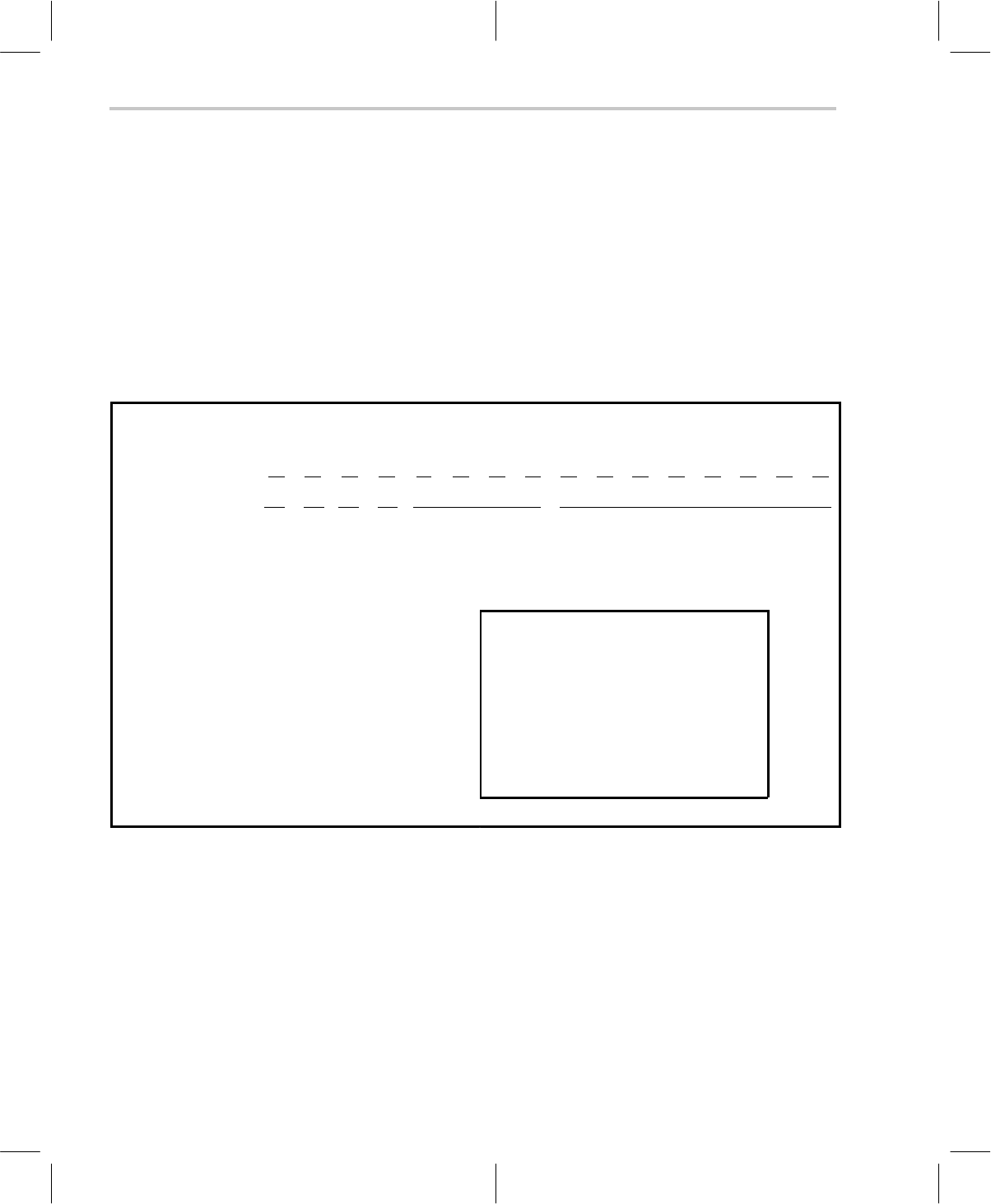

IntGenCtrl register

address 0x38 (16-bit wide location)

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

CE AR PD EP E2 E1 S2 S1 D5 D4 PF D3 D2 T2 T1 DA

low

priority

high

priority

0x0000 : State after RESET low

Interrupt mask register

CE : Comparator enable

AR : ARM bit

PD : Pulse-density clock: PDMCD

EP : Enable pullup resistors on port F

D5 : port D

5

falling-edge

D4 : port D

4

rising-edge

PF : any port F falling-edge

D3 : port D

3

falling-edge

E2 : Enable TIMER2 (1 value starts timer)

E1 : Enable TIMER 1 (1 value starts timer)

S2 : Clock source for TIMER2 (0 = MC/2, 1 = ref Osc)

S1 : Clock source for TIMER1 (0 = MC/2, 1 = ref Osc)

D2 : port D

2

rising-edge

T2 : TIMER2 underflow

T1 : TIMER1 underflow

DA : DAC timer underflow

(1 value enables interrupt service)

The remaining bits in the IntGenCtrl have various control functions which are

not directly related to the interrupt system. Four of these are related to the timer

functions. Bits 8 and 9 are used to select the clock sources which govern the

rates of TIMER1 and TIMER2. Clearing bit 8 chooses 1/2 MC as the source

for TIMER1 (i.e., the TIMER runs at one-half the frequency of the Master

Clock). Setting bit 8 chooses the reference oscillator (RTO or CRO) as the

source for TIMER1. (The same applies for bit 9 and TIMER2.) Bits 10 and 11

are used to enable TIMER1 and TIMER2, respectively. Setting bit 10 starts

TIMER1, and clearing bit 10 stops TIMER1. (The same applies for bit 11 and

TIMER2).