Instruction Classification

4-36

4.4.5 Class 5 Instructions: Memory Reference

Class 5 instructions provide transfer to and from data memory and all registers

except accumulators and Rx which are included in classes 1 and 4. The

registers referenced for both read and write operations are the multiplier

register (MR), the product high register (PH), the shift value register (SV), the

status register (STAT), the top of stack (TOS), the string register (STR), and

the four accumulator pointer registers AP0 to AP3. The data pointer register

(DP) is read only since its value is established by lookup table instructions. The

RPT n (repeat) instruction is write only since repeated instructions cannot be

interrupted. IRET and RET instructions are read only operations for popping

the stack and are included in this class because the stack is memory mapped.

Also included in this class are four flag instructions that modify flag memory

and two instructions that multiply memory by MR, storing the results in the PH

register.

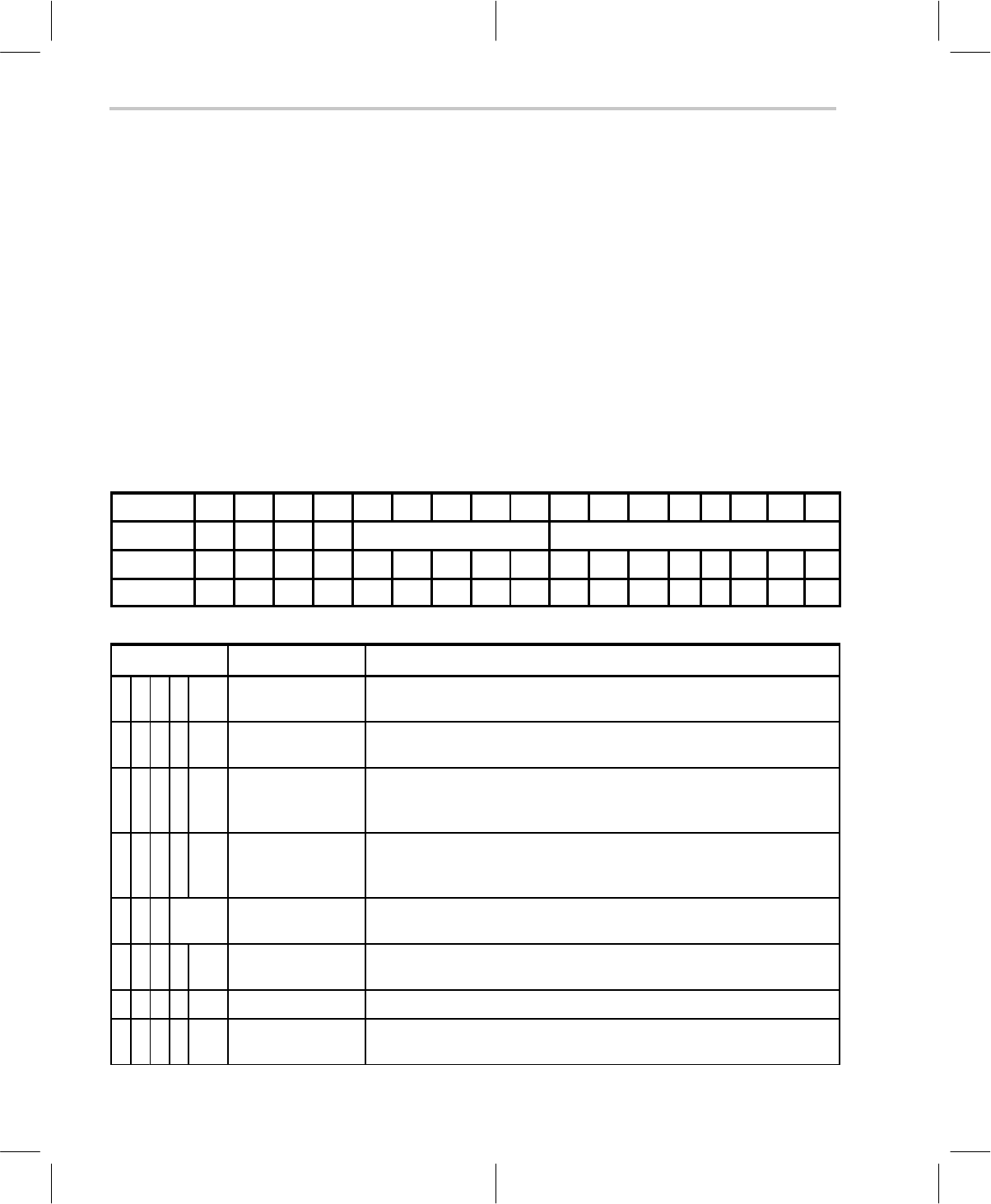

Table 4–26. Class 5 Instruction Encoding

Bit 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Class 5 1 1 0 1 C5 adrs

RET 1 1 0 1 1 1 1 0 0 0 1 1 1 1 1 1 0

IRET 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0

Table 4–27. Class 5 Instruction Description

C5 Mnemonic Description

0 0 0 0 0 MOV {adrs}, SV Store SV in the data memory location referred by addressing mode

{adrs}, zero filled on upper 12 bits. Transfer status is modified.

0 0 0 0 1 MOV {adrs}, PH Store the PH in the data memory location referred by addressing mode

{adrs}. Transfer status is modified.

0 0 0 1 0 MOV {adrs}, STAT Store the status (STAT) register contents to the data memory location

referred by addressing mode {adrs} (17 bits including TAG). No

modification of status.

0 0 0 1 1 MOV {adrs}, STR Store string (STR) register contents to data memory location referred by

addressing mode {adrs}, zero filled on upper 8 bits. Transfer status is

modified.

0 0 1 n MOV {adrs}, APn Store the accumulator pointer (APn) register to the data memory location

in {adrs}. The upper 10 bits are zero filled. Transfer status is modified.

0 1 0 0 0 MOV {adrs}, MR Store the contents of the multiplier (MR) register in {adrs}. Transfer

status is modified.

0 1 0 0 1 Reserved

0 1 0 1 0 MOV {adrs}, DP Store the data pointer (DP) register contents to the location referred by

{adrs}. Transfer status is modified.