Computation Unit

2-7MSP50C6xx Architecture

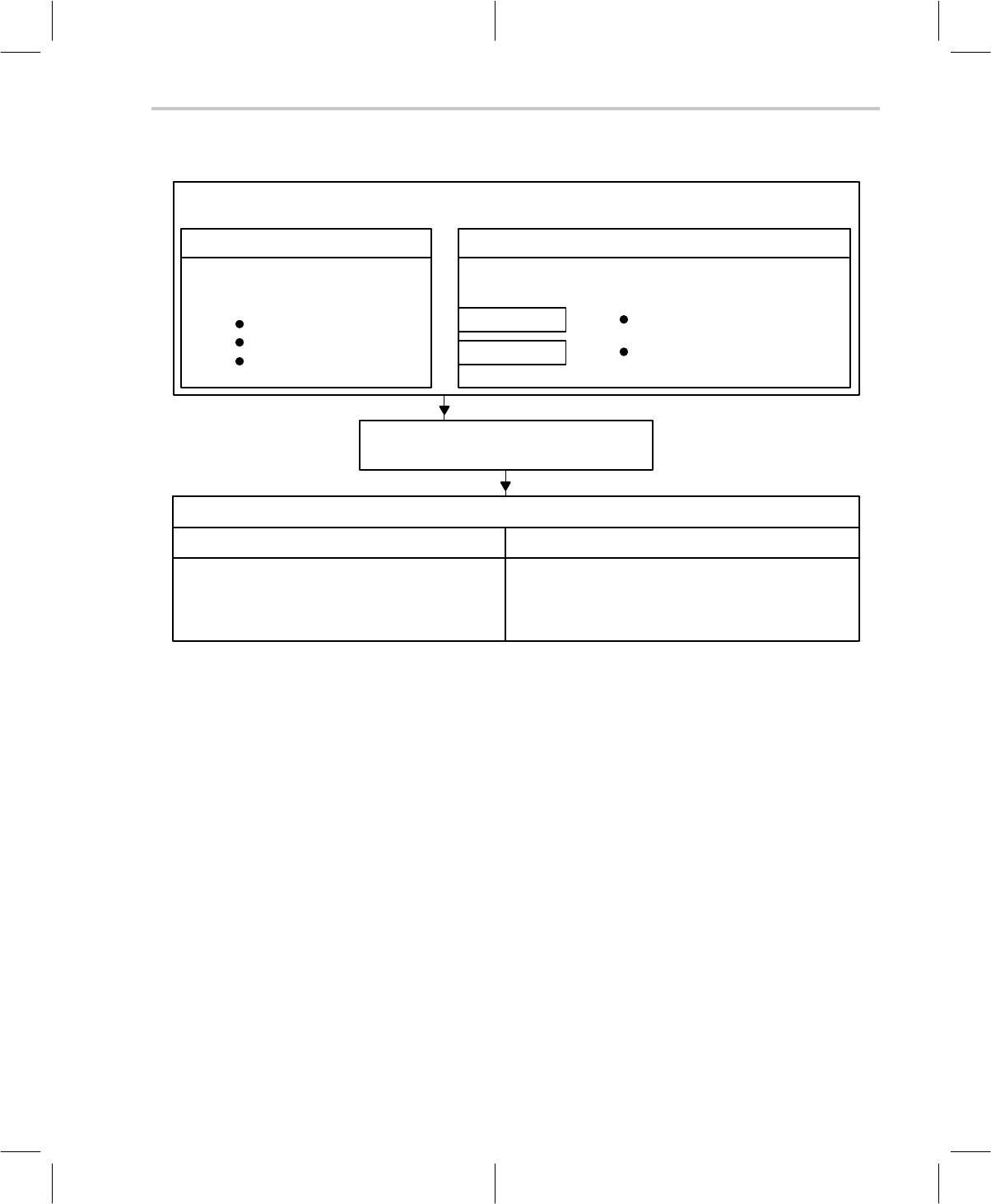

Figure 2–3. Overview of the Multiplier Unit Operation

MULTIPLIER UNIT INPUTS

Multiplicand 16-bit

- latched in a write-only register

from one of the following sources ...

Data Memory

Accumulator

Offset Accumulator

X Multiplier

- writeable and readable by Data Memory

as one of the following ...

Multiplier Register†

Shift Value Register

or

MULTIPLYING: 16-bit

4-bit

SHIFTING:

(MR)

(SV)

MULTIPLIER UNIT

performs multiplication and barrel shifting

MULTIPLIER UNIT INPUTS

MSB 16-bit LSB 16-bit

- readable and writeable by Data Memory - a simulated register: PL is realized in ALU-A

- readable and writeable by ALU-A

(PH) Product High (PL) Product Low

†

Also write-able by Program Memory

2.2.2 Arithmetic Logic Unit

The arithmetic logic unit is the focal point of the computational unit, where data

can be added, subtracted, and compared. Logical operations can also be

performed by the ALU. The basic hardware word-length of the ALU is 16 bits;

however, most ALU instructions can also operate on strings of 16-bit words

(i.e., a series or array of values). The ALU operates in conjunction with a

flexible, 16-bit accumulator register block. The accumulator register block is

composed of thirty-two, 16-bit registers which further enhances execution and

promotes compact code.

The ALU has two distinct input paths, denoted ALU-A and ALU-B (see

Figure-2–4). The ALU-A input selects between all zeros, the internal databus,

the product high register (PH), the product low (PL), or the offset output of the

accumulator register block. The ALU-B input selects between all zeros and the

output from the accumulator register block.