Instruction Classification

4-34

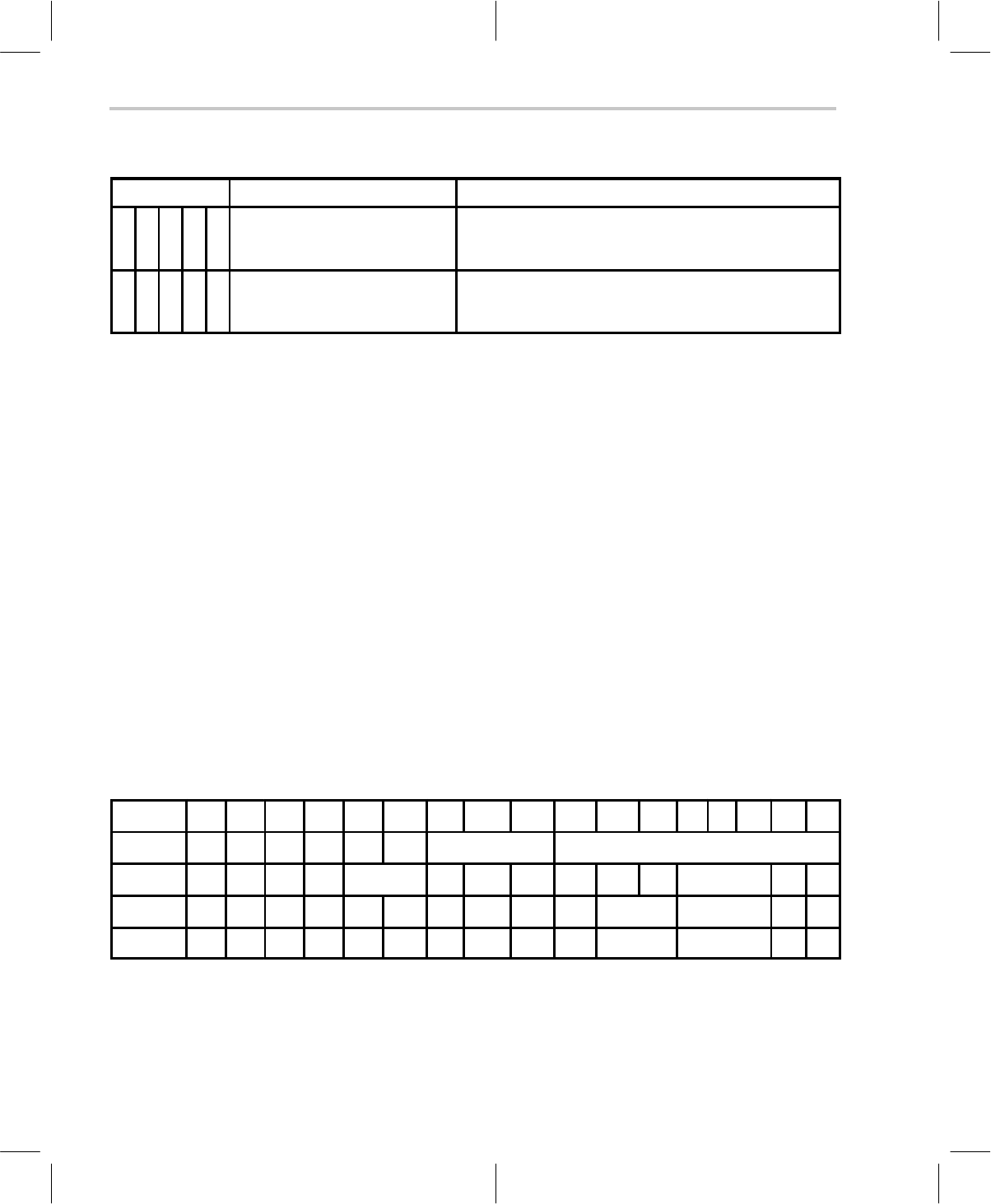

Table 4–20. Class 3 Instruction Description (Continued)

C3 Mnemonic Description

1 1 1 1 0 MUL An[~] [, next A]

MULS An[~]

Multiply MR register by accumulator (A~=1) or offset

accumulator (A~=0) and latch the rounded upper 16 bits of

the resulting product into the PH register.

1 1 1 1 1 SHL An[~] [, next A]

SHLS An[~]

Barrel shift the accumulator (A~=1) or offset accumulator

(A~=0) value n bits left (n stored in SV register). Store the

upper 16 bits of the 32-bit shift result to PH.

4.4.4 Class 4 Instructions: Address Register and Memory Reference

Class 4 instructions operate on the indirect register, Rx, that exists in the ad-

dress unit (ADU). Even though the last three registers (R5–R7) are special

(INDEX, PAGE, and STACK), class 4 instructions uniformly apply to all regis-

ters. Subclass 4a provides transfers to and from memory. In indirect mode, any

one auxiliary register can serve as the address for loading and storing the con-

tents of another.

Subclass 4b instructions provide some basic arithmetic operations between

referenced auxiliary register and short 8-bit constants from program memory.

These instructions are included to provide efficient single cycle instructions for

loop control and for software addressing routines.

Subclass 4c provide basic arithmetic operations between the referenced auxil-

iary register and 16-bit constants from program memory. These instruction re-

quire 2 instruction cycles to execute.

Also a compare to R5 (INDEX) is provided for efficient loop control where the

final loop counter value is not chosen to be zero.

Table 4–21. Class 4a Instruction Encoding

Bit 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Class 4a 1 1 1 1 0 C4a R adrs

Class 4b 1 0 1 1 C4b k4 k3 k2 k7 k6 k5 R k1 k0

Class 4c 1 1 1 1 1 1 1 0 0 0 C4c R x x

Class 4d 1 1 1 1 1 1 1 0 0 1 C4d R x x