Execution Timing

2-40

2.11 Execution Timing

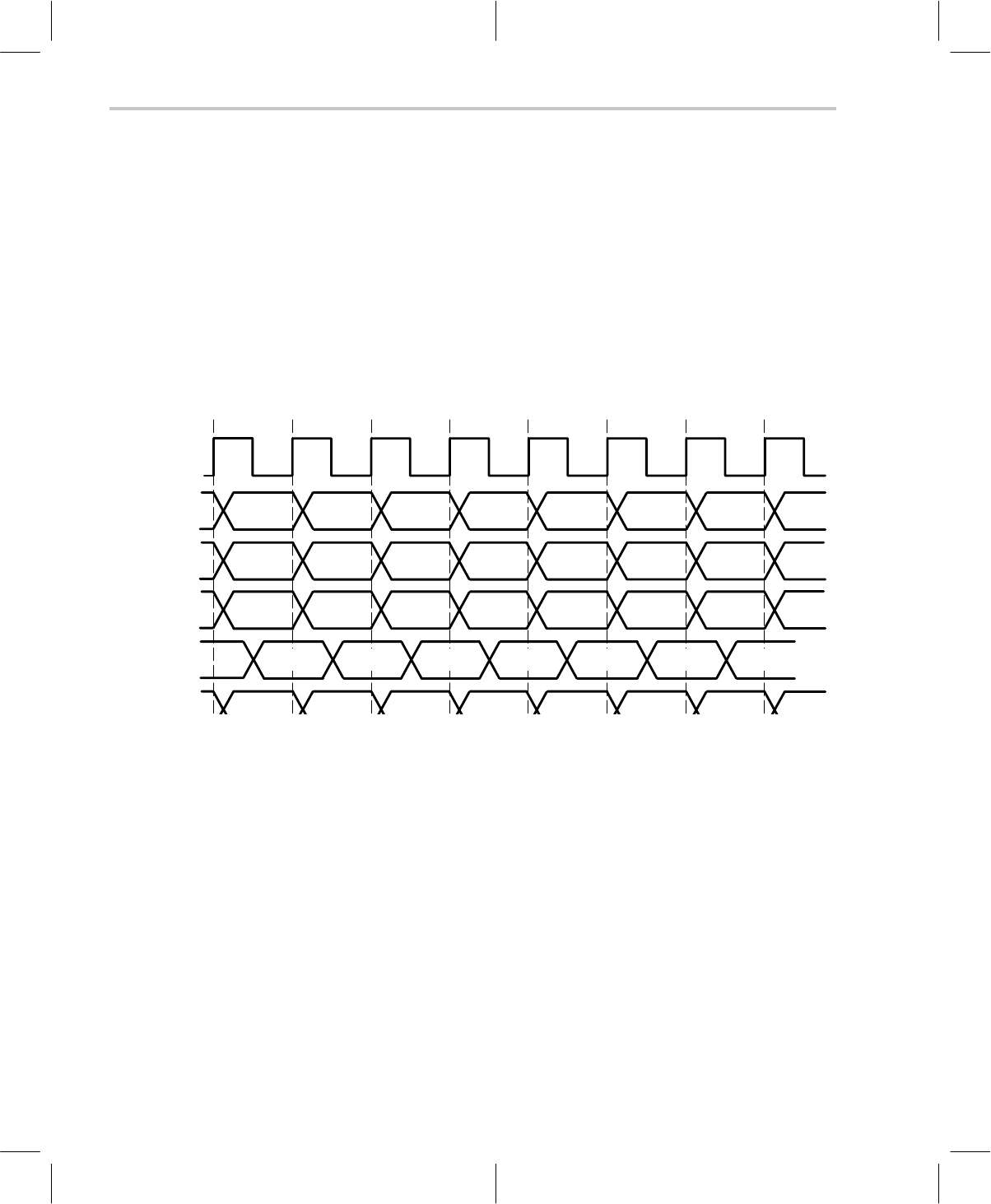

For executing program code, the C6xx’s core processor has a three-level

pipeline. The pipeline consists of instruction fetch, instruction decode, and

instruction execution. A single instruction cycle is limited to one program Fetch

plus one data memory read or write. The master clock consists of two phases

with non-overlap protection. A fully static implementation eliminates pre-

charge time on busses or in memory blocks. This design also results in a very

low power dissipation. Figure 2–10 illustrates the basic timing relationship

between the master clock and the execution pipeline.

Figure 2–10. Instruction Execution and Timing

N

N+1 N+2

N+3

N+4

N+5 N+6

N+7

FETCH

CLOCK

N–1

N N+1

N+2

N+3

N+4 N+5

DECODE

N–2

N–1 N

N+1

N+2

N+3 N+4

N+5

EXEC

N–1

N N+1

N+2

N+3

N+4 N+5

DATA ADD

N

N+1 N+2

N+3

N+4

N+5 N+6

N+7

PC ADD