AMD Confidential

User Manual November 21

st

, 2008

Appendix A 223

Interrupt to task-gate is not implemented. An attempt to execute an interrupt to

task-gate results in a „FeatureNotImplemented‟ exception and the simulation will

be stopped.

When delivering an exception in an attempt to deliver a hardware interrupt the

simulation will not push the resume-flag (RF) onto the stack.

Always clears VM, NT, TF, and RF bits in rFLAGS.

A.6.3.2 IRET – Return from Interrupt

Opcode

Instruction

Description

CF

IRET, IRETD,

IRETQ

Return from interrupt

The simulator does not support nested task-switching using the rFLAGS nested-task bit

(NT) and the TSS back-link field. An interrupt return (IRET) to the previous task (nested-

task) will result in a „FeatureNotImplemented‟ exception and the simulation will be

stopped.

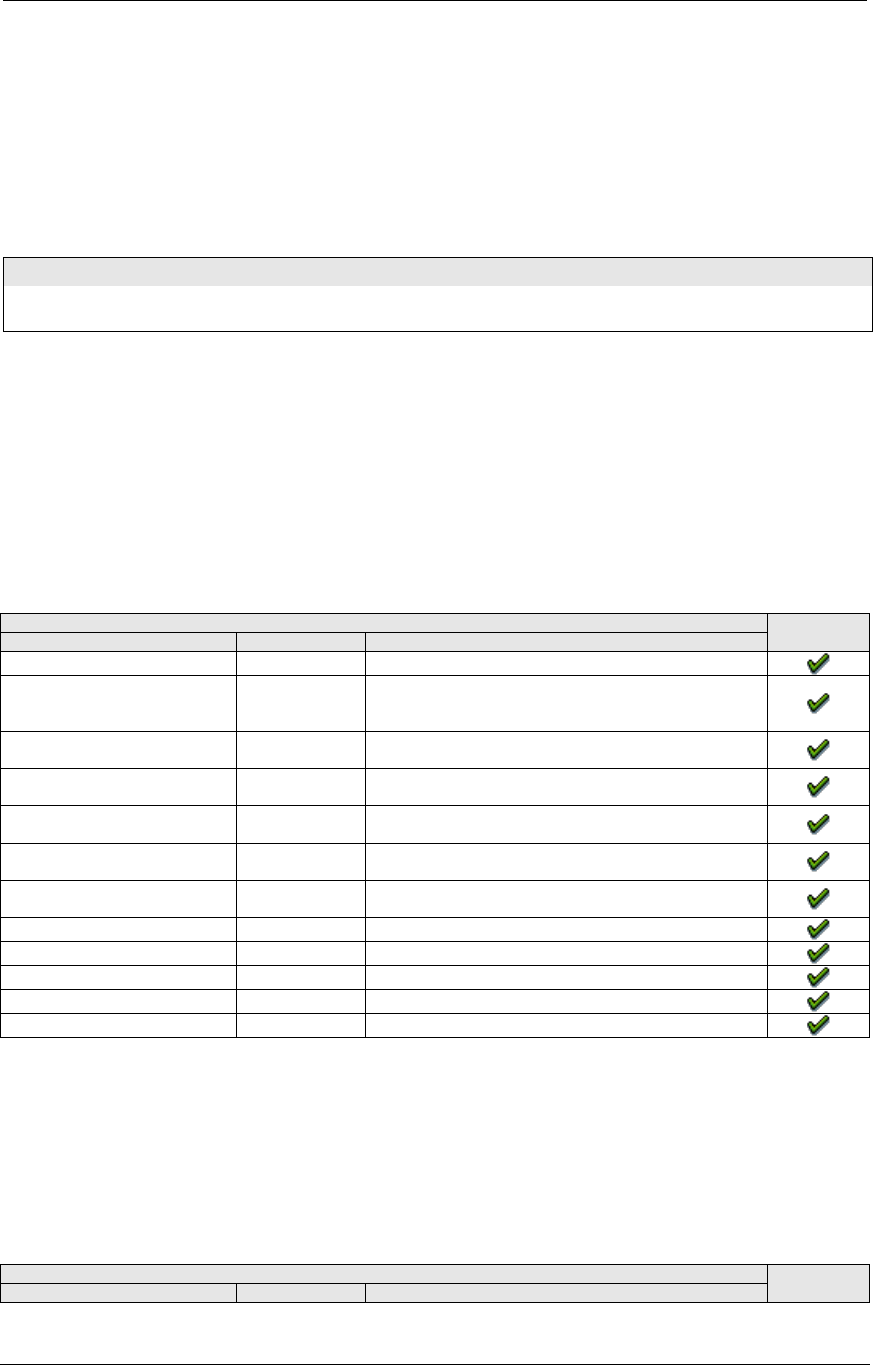

A.6.4 Virtualization Instruction Reference

For more information on Virtualization Technology, see AMD Publication #33047,

AMD64 Virtualization Technology.

Instruction

Supported

Mnemonic

Opcode

Description

CLGI

0F 01 DD

Clear Global Interrupt Flag.

INVLPGA

0F 01 DF

Invalidates the TLB mapping for the

virtual page specified in rAX and the

ASID specified in ECX.

MOV reg32,CR8

F0 20 /r

Alternate notation for move from CR8 to

register.

MOV reg64,CR8

F0 20 /r

Alternate notation for move register to

CR8.

MOV CR8,reg32

F0 22 /r

Alternate notation for move from CR8 to

register.

MOV CR8,reg64

F0 22 /r

Alternate notation for move register to

CR8.

SKINIT

0F 01 DE

Secure initialization and jump, with

attestation.

STGI

0F 01 DC

Set Global Interrupt Flag.

VMLOAD

0F 01 DA

Load State from VMCB.

VMCALL

0F 01 D9

Call VMM.

VMRUN

0F 01 D8

Run Virtual Machine.

VMSAVE

0F 01 DB

Save State to VMCB.

A.6.5 64-Bit Media Instruction Reference

These instructions described in this section operate on data located in the 64-bit MMX

registers. Most of the instructions operate in parallel on sets of packed elements called

vectors, although some operate on scalars. The instructions define both integer and

floating-point operations, and include the legacy MMX instructions and the AMD

extensions to the MMX instruction set.

Instruction

Supported

Mnemonic

Opcode

Description