AMD Confidential

User Manual November 21

st

, 2008

224 Appendix A

Instruction

Supported

Mnemonic

Opcode

Description

CVTPD2PI mmx,xmm2/m128

66 0F 2D /r

Converts packed double-precision

floating-point values in an XMM

register or 128-bit memory location to

packed doubleword integers values in

the destination MMX™ register.

CVTPI2PD xmm,mmx/m64

66 0F 2A /r

Converts two packed doubleword integer

values in a MMX™ register or 64-bit

memory location to two packed double-

precision floating-point values in the

destination XMM register.

CVTPI2PS mmx,xmm2/m128

0F 2A /r

Converts packed doubleword integer

values in a MMX™ register or 64-bit

memory location to single-precision

floating-point values in the

destination XMM register.

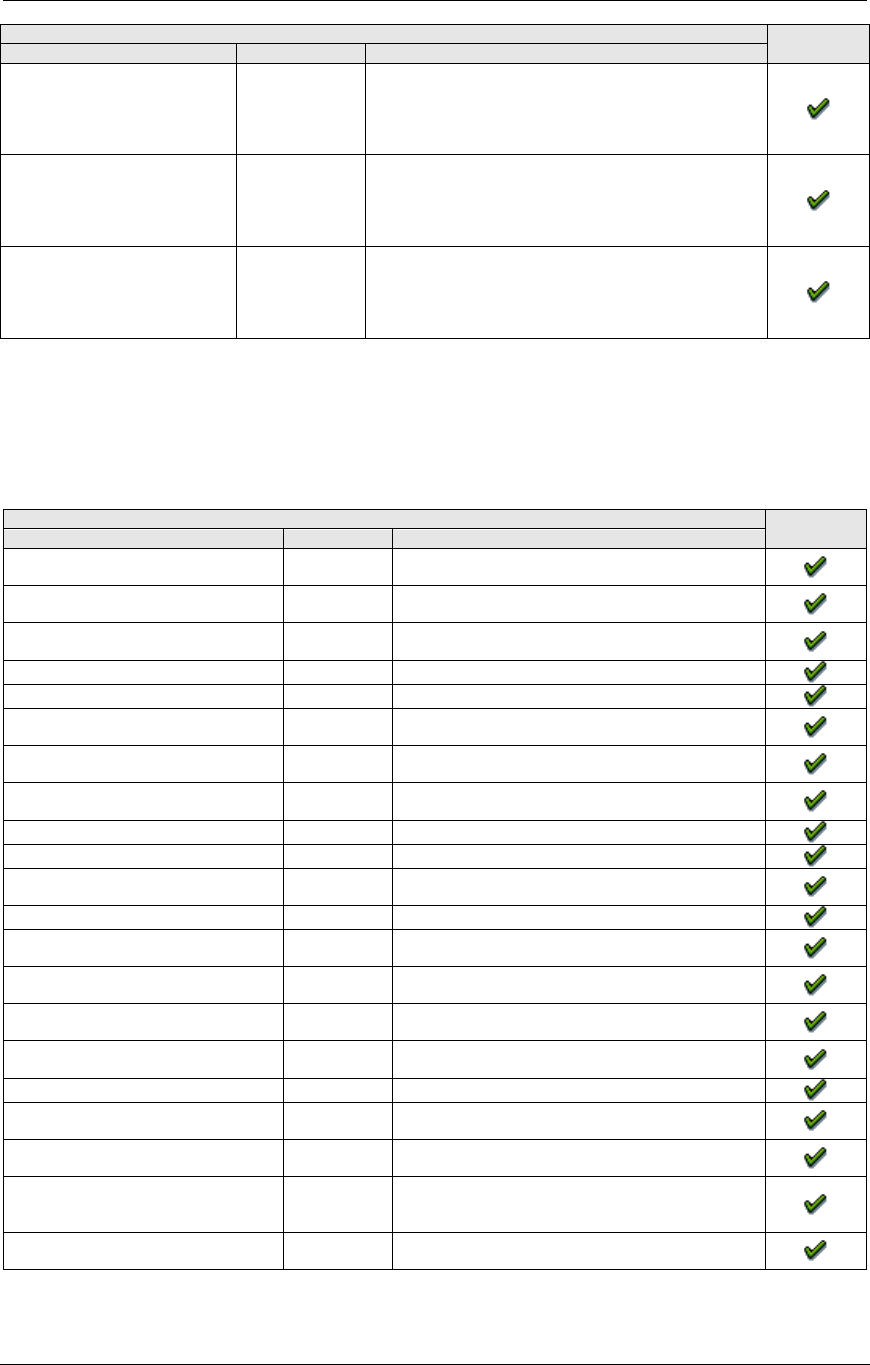

A.6.6 3DNow!™ Instruction Set

This chapter describes the 3DNow! Instruction Set that the simulator supports and

simulates. 3DNow! Technology is a group of new instructions that opens the traditional

processing bottlenecks for floating-point-intensive and multimedia applications.

Instruction

Supported

Mnemonic

Opcode

Description

FEMMS

0F 0E

Fast Enter/Exit of the MMX or

floating-point state.

PAVGUSB mmreg1,mmreg2/m64

0F 0F /BF

Average of unsigned packed 8-bit

values.

PF2ID mmreg1,mmreg2/m64

0F 0F /1D

Converts packed floating-point

operand or packed 32-bit integer.

PFACC mmreg1,mmreg2/m64

0F 0F /AE

Floating-point accumulate.

PFADD mmreg1,mmreg2/m64

0F 0F /9E

Packed, floating-point addition.

PFCMPEQ mmreg1,mmreg2/m64

0F 0F /B0

Packed floating-point comparison,

equal to.

PFCMPPGE mmreg1,mmreg2/m64

0F 0F /90

Packed floating-point comparison,

greater than or equal to.

PFCMPGT mmreg1,mmreg2/m64

0F 0F /A0

Packed floating-point comparison,

greater than.

PFMAX mmreg1,mmreg2/m64

0F 0F /A4

Packed floating-point maximum.

PFMIN mmreg1,mmreg2/m64

0F 0F /94

Packed floating-point minimum.

PFMUL mmreg1,mmreg2/m64

0F 0F /B4

Packed floating-point

multiplication.

PFRCP mmreg1,mmreg2/m64

0F 0F /96

Packed floating-point approximation.

PFRCPIT1 mmreg1,mmreg2/m64

0F 0F /A6

Packed floating-point reciprocal,

first iteration step.

PFRCPIT2 mmreg1,mmreg2/m64

0F 0F /B6

Packed floating-point reciprocal,

second iteration step.

PFRSQIT1 mmreg1,mmreg2/m64

0F 0F /A7

Packed floating-point reciprocal,

square root, first iteration step.

PFRSQRT mmreg1,mmreg2/m64

0F 0F /97

Packed floating-point reciprocal,

square root approximation.

PFSUB mmreg1,mmreg2/m64

0F 0F /9A

Packed, floating-point subtraction.

PFSUBR mmreg1,mmreg2/m64

0F 0F /AA

Packed, floating-point reverse

subtraction.

PI2FD mmreg1,mmreg2/m64

0F 0F /0D

Packed 32-bit integer to floating-

point conversion.

PMULHRW mmreg1,mmreg2/m64

0F 0F /B7

Multiply signed packed 16-bit values

with rounding and store the high 16

bits.

PREFETCH/PREFETCHW

0F 0D

Prefetch processor cache line into

L1 data cache (Dcache).

Table 15-10: 3DNow!™ Instruction Reference