ML361 Virtex-II Pro Memory Board www.xilinx.com 15

UG060 (v1.2) November 8, 2007

Block Descriptions

R

166 MHz LVDS Test Clock

The LVDS test clock is a Pletronics SM7745DW-100.0M clock oscillator with a single-ended

output. This oscillator runs at 166 MHz ± 50 PPM with an operating voltage of 2.5 V ± 5%.

FPGA pins E17 and D17 in Bank 1 serve as the CLK_166_LVDSP and CLK_166_LVDSN

inputs, respectively.

SMA Clock

Two SMA connectors are provided for the input of an off-board differential clock. The

traces from the SMAs are run as a pair to the FPGA where they are terminated with a

100 ohm resistor. AK18 serves as the CLK_SMAP input, and AL18 serves as the

CLK_SMAN input for the SMA connector pair.

User I/Os

This subsection describes the devices that connect to the User I/Os of the ML361 board.

Mictor Connectors

The FPGA interfaces to two 38-pin Mictor connectors. They can be used to hook up to a

logic analyzer. All signals from the FPGA to the connectors are matched closely. Refer to

the Xilinx data sheets in Appendix A, “Related Documentation,” for more information.

GPIO

The ML361 board contains 16 general-purpose I/Os (GPIOs), which are accessible through

two 2 x 8 0.100" pin headers (see Table 2-1 and Table 2-2). The even-numbered pins on each

header are connected to ground. The GPIO header pins can be accessed through I/Os in

Bank 0.

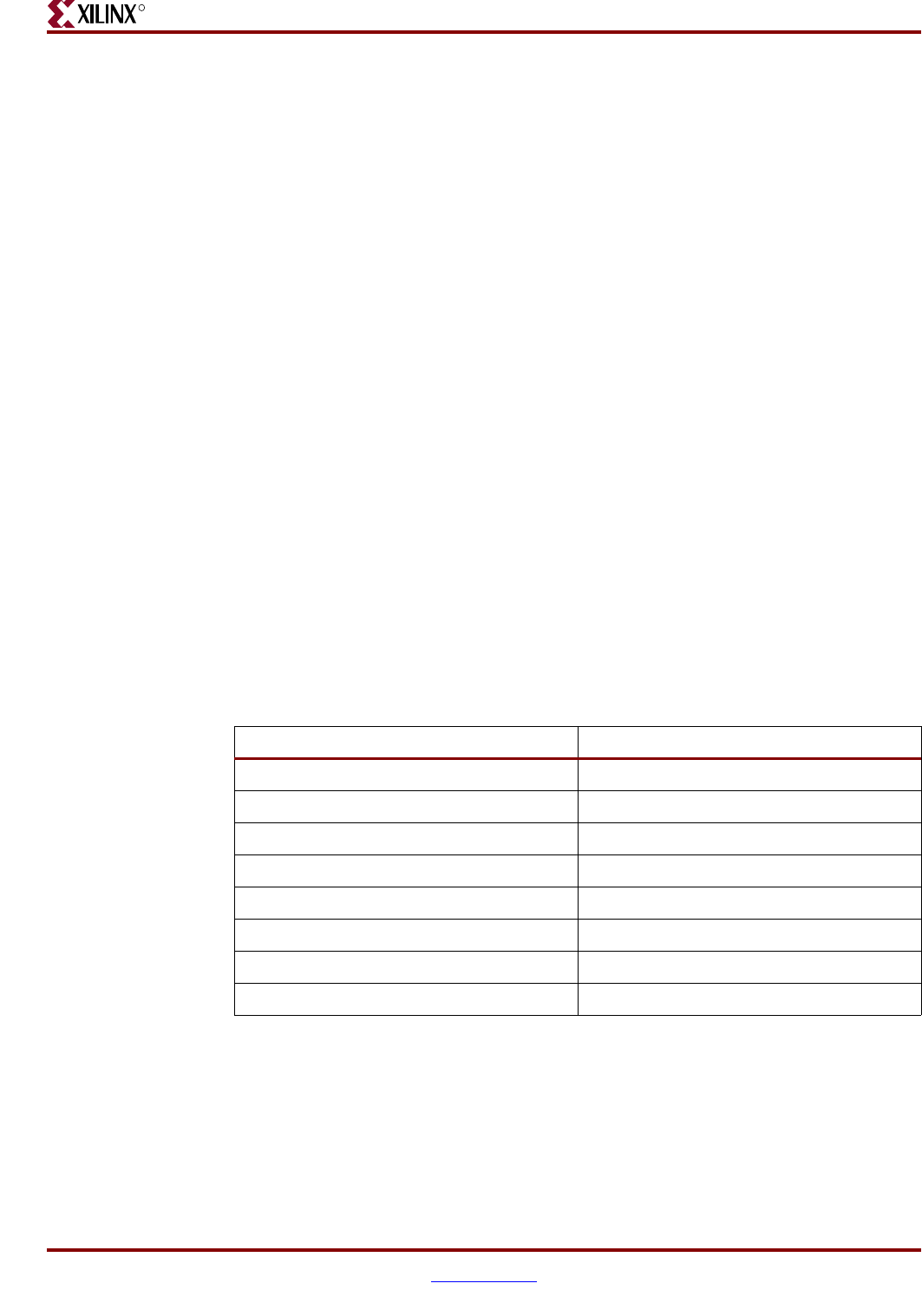

Table 2-1: GPIO Header 1

GPIO Pin # FPGA I/O Pin

G00 F22

G01 E22

G02 E25

G03 D25

G04 H21

G05 D22

G06 D23

G07 D24