ML361 Virtex-II Pro Memory Board www.xilinx.com 65

UG060 (v1.2) November 8, 2007

R

Chapter 5

Board Layout Guidelines

This chapter provides information on decoupling capacitors, ground signals, and PCB

layout.

Decoupling Guidelines

This section lists the decoupling capacitors used with the major components of the ML361

board. Refer to the board schematics for exact placement.

Table 5-1 lists the decoupling capacitors for the Virtex-II Pro FPGA. Refer to the Xilinx

XAPP623

application note for the methodology. A balanced decoupling network is

implemented for each bank, VCCI, VAUX, and VREF.

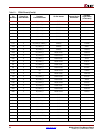

Table 5-1: FPGA Decoupling Capacitors

Pin(s) Capacitor Value Distribution

VCCI

1 capacitor per

pin, in a

balanced

decoupling

network.

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 10

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 5

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 6

10 µF ceramic capacitor, 1206 16V Z5U –20/+20% 3

330 µF solid tantalum capacitor, 6.3V 2

VA UX

1 capacitor per

pin, in a

balanced

decoupling

network.

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 4

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 3

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 3

10 µF ceramic capacitor, 1206 16V Z5U –20/+20% 1

330 µF solid tantalum capacitor, 6.3V 1

Bank 2

39 SSTL2_II

20 SSTL2_I

Budget = (61/120) = .51 x 12 = 7 caps

0.039 µF ceramic capacitor, 0402 10V X7R –20/+20% 2

0.22 µF ceramic capacitor, 0603 10V X7R –20/+20% 1

1 µF ceramic capacitor, 0603 6V X7R –20/+20% 1

330 µF solid tantalum capacitor, 6.3V 1