28 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Chapter 4: Signal Integrity Recommendations and Simulations

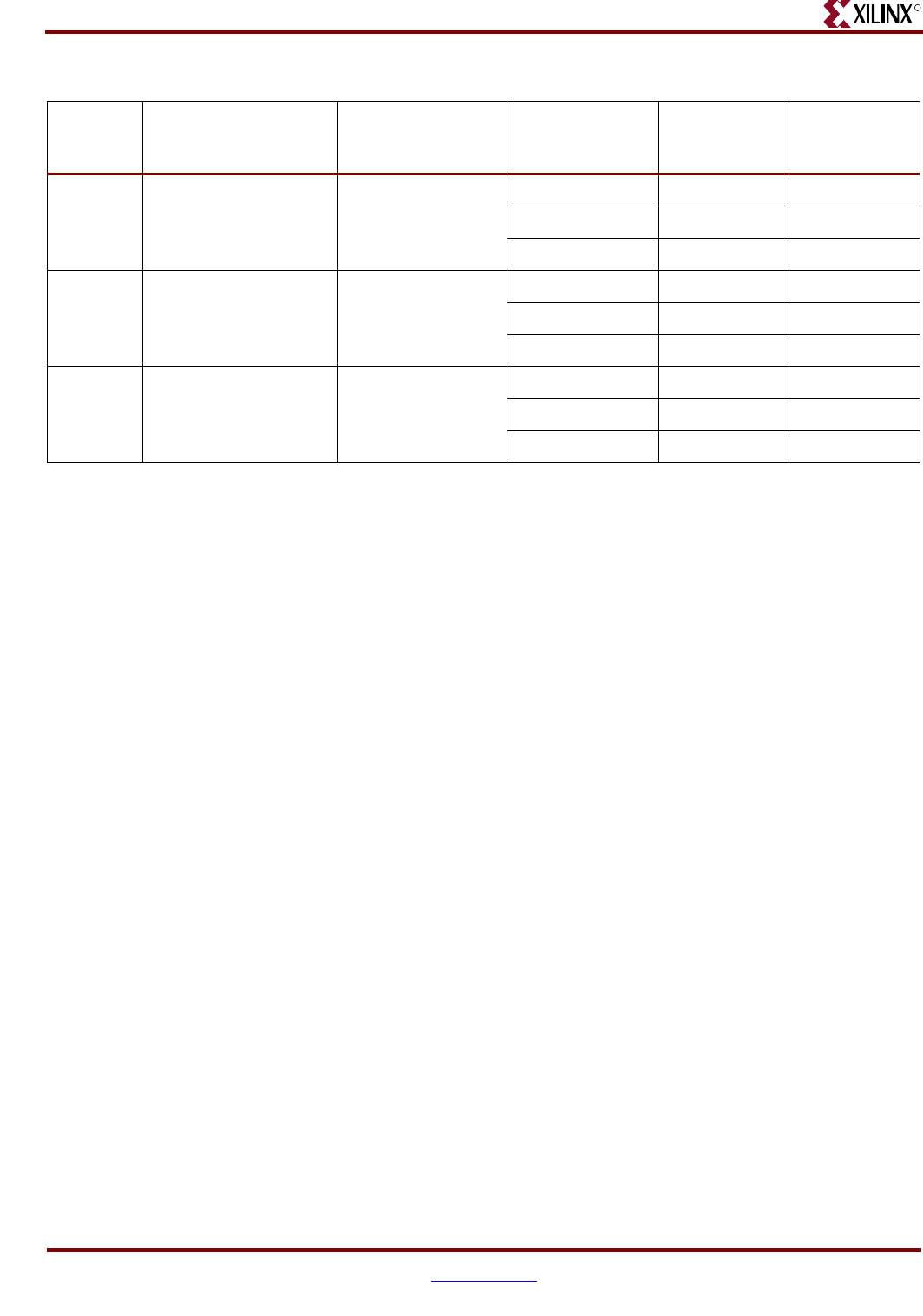

R

3 Address/control Middle component Typical 49.23/51.49 NA

Slow weak 49.22/50.64 NA

Fast strong 48.94/51.2 NA

4 Clock Last component Typical 48.1/52.04 NA

Slow weak 48.66/51.48 NA

Fast strong 48.1/51.48 NA

5 Data Last component Typical 47.24/52.62 48.64/51.78

Slow weak 47.52/52.06 49.52/50.64

Fast strong 46.4/52.9 48.38/51.76

Table 4-3: Duty Cycle Summary

No. Signal DDR Component Case

Duty Cycle

Measured at

Memory(%)

Duty Cycle

Measured at

FPGA (%)