88 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

R

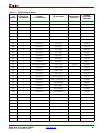

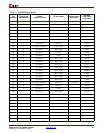

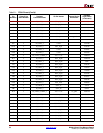

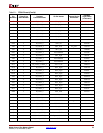

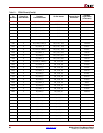

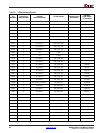

K30 7 IO_L33N_7 dimm_dq65 8267.43

M26 7 IO_L32P_7 dimm_dq66 4123.3

M25 7 IO_L32N_7 dimm_dq67 3062.48

H34 7 IO_L31P_7 dimm_dq68 13451.41

H33 7 IO_L31N_7 dimm_dq69 12137.04

F31 7 IO_L06P_7 dimm_dq70 11858.77

F30 7 IO_L06N_7 dimm_dq71 10666.81

J28 7 IO_L05P_7 dimm_a10 no_pin8 7292.33

J27 7 IO_L05N_7 dimm_a11 6469.14

E34 7 IO_L04P_7 dimm_a12 15132.61

E33 7 IO_L04N_7/VREF_7 Vref = 1.3V 13663.12

E32 7 IO_L03P_7 dimm_sa0 13396.34

E31 7 IO_L03N_7 dimm_sa1 11802.85

F28 7 IO_L02P_7 dimm_sa2 11146.23

F27 7 IO_L02N_7 dimm_scl 12438.46

D34 7 IO_L01P_7/VRN_7 Pullup to 2.6V for DCI 15547.77

D33 7 IO_L01N_7/VRP_7 Pulldown to GND for DCI 14050.12

J26 PROG_B PROGRAMn

K25 HSWAP_EN HSWAP

K26 DXP

G27 DXN

A29 TXNPAD4

A28 TXPPAD4

A27 RXPPAD4

A26 RXNPAD4

A21 TXNPAD6

A20 TXPPAD6

A19 RXPPAD6

A18 RXNPAD6

A17 TXNPAD7

A16 TXPPAD7

A15 RXPPAD7

A14 RXNPAD7

Table B-1: FPGA Pinout (Cont’d)

Pin

Numbers

Virtex-II Pro

Bank Number

Package

Functional Name

I/O Pin Names

Internal Script

Information

Package

Flight Times

(in microns)