ML361 Virtex-II Pro Memory Board www.xilinx.com 89

UG060 (v1.2) November 8, 2007

R

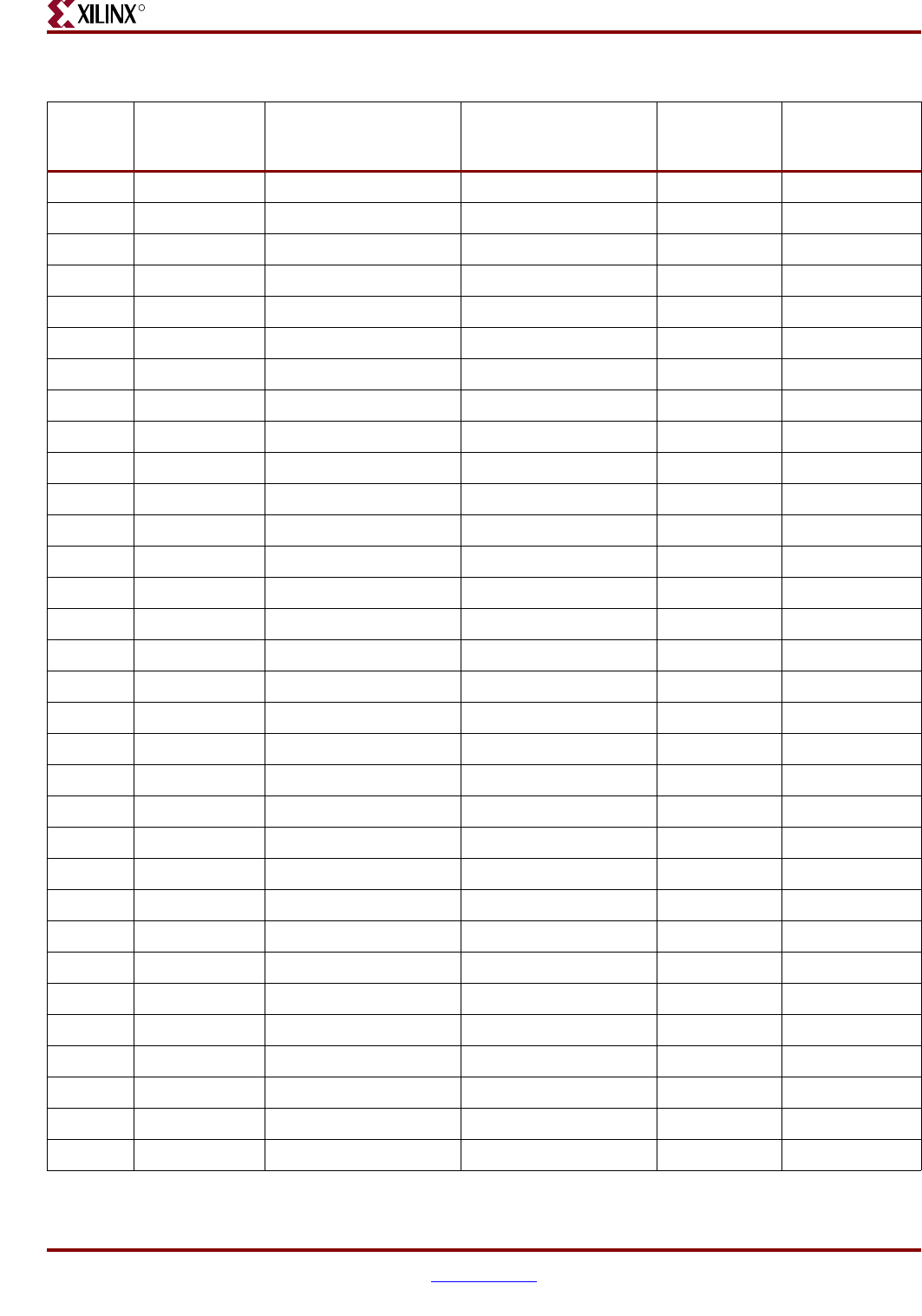

A9 TXNPAD9

A8 TXPPAD9

A7 RXPPAD9

A6 RXNPAD9

G8 RSVD

K9 VBATT

K10 TMS TMS

J9 TCK TCK

H7 DO TDO.FPGA.to.TDO.PORT

AE9 CCLK FPGA.CCLK

AF9 PWRDWN_B PWRDWN

AE10 DONE DONE

AP6 RXNPAD16 RXNPAD18

AP7 RXPPAD16 RXPPAD18

AP8 TXPPAD16 TXPPAD18

AP9 TXNPAD16 TXNPAD18

AP14 RXNPAD18 RXNPAD18

AP15 RXPPAD18 RXPPAD18

AP16 TXPPAD18 TXPPAD18

AP17 TXNPAD18 TXNPAD18

AP18 RXNPAD19

AP19 RXPPAD19

AP20 TXPPAD19

AP21 TXNPAD19

AP26 RXNPAD21

AP27 RXPPAD21

AP28 TXPPAD21

AP29 TXNPAD21

AE25 M2 M2

AF26 M0 M0

AE26 M1 M1

H28 TDI TDO.PROM.to.TDI.FPGA

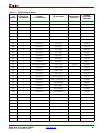

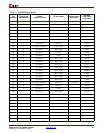

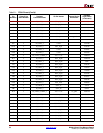

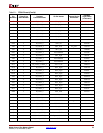

Table B-1: FPGA Pinout (Cont’d)

Pin

Numbers

Virtex-II Pro

Bank Number

Package

Functional Name

I/O Pin Names

Internal Script

Information

Package

Flight Times

(in microns)