72 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

R

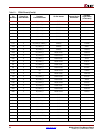

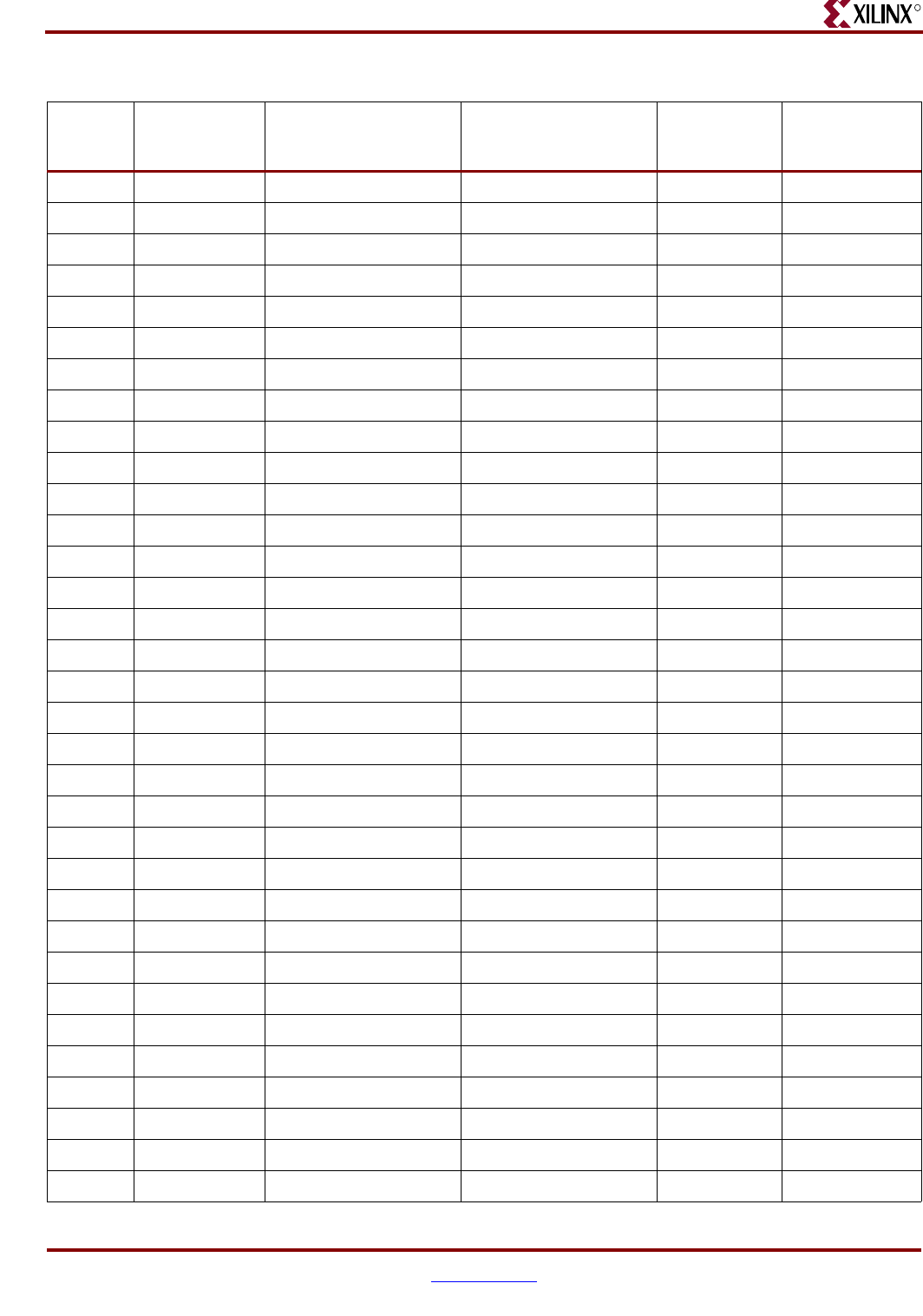

K21 0 IO_L39N_0 GND 5505.04

J21 0 IO_L39P_0 GND 4965.14

F22 0 IO_L43N_0 GPIO00 7541.44

E22 0 IO_L43P_0 GPIO01 8910.89

E25 0 IO_L44N_0 GPIO02 12735.3

D25 0 IO_L44P_0 GPIO03 13832.18

H21 0 IO_L45N_0 GPIO04 6364.26

G21 0 IO_L45P_0/VREF_0 GPIO05 7704.24

D22 0 IO_L46N_0 GPIO06 9988.1

D23 0 IO_L46P_0 GPIO07 11050.72

D24 0 IO_L47N_0 DISPLAY1G 12302.96

C24 0 IO_L47P_0 DISPLAY1F 13516.13

K20 0 IO_L48N_0 DISPLAY1E 3126.3

J20 0 IO_L48P_0 DISPLAY1D 4150.17

F21 0 IO_L49N_0 DISPLAY1C 7682.05

E21 0 IO_L49P_0 DISPLAY1B 8634.04

C21 0 IO DISPLAY1A 13499.9

C22 0 IO DISPLAY2G 15061.08

L19 0 IO_L54N_0 DISPLAY2F 2263.39

K19 0 IO_L54P_0 DISPLAY2E 3226.4

G20 0 IO_L55N_0 DISPLAY2D 6227.05

F20 0 IO_L55P_0 DISPLAY2C 7549.54

D21 0 IO_L56N_0 DISPLAY2B 10983.43

D20 0 IO_L56P_0 DISPLAY2A 10275.3

J19 0 IO_L57N_0 GND 3969.14

H19 0 IO_L57P_0/VREF_0 GND 5173.85

G19 0 IO_L67N_0 GND 6064.32

F19 0 IO_L67P_0 GND 8063.93

E19 0 IO_L68N_0 GND 9549.27

D19 0 IO_L68P_0 GND 10957.97

L18 0 IO_L69N_0 LED1 2444

K18 0 IO_L69P_0/VREF_0 LED2 3320.11

G18 0 IO_L73N_0 LED3 5890.16

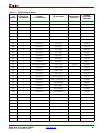

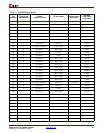

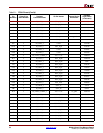

Table B-1: FPGA Pinout (Cont’d)

Pin

Numbers

Virtex-II Pro

Bank Number

Package

Functional Name

I/O Pin Names

Internal Script

Information

Package

Flight Times

(in microns)