ML361 Virtex-II Pro Memory Board www.xilinx.com 27

UG060 (v1.2) November 8, 2007

Duty Cycle Summary

R

• There is a total of 4.9 inches of trace from the FPGA to the last component assuming

the DDR memory components are 0.6 inch apart.

Microstrip is used to model the transmission lines for the first DDR component. All other

DDR components use Buried Microstrip to model the transmission lines.

Terminations and Transmission Lines for the DIMM

Data and Clock Signals (DQ, DQS, DM, CLK)

For these DIMM signals, the terminations at the FPGA and memory consist of a 50Ω

parallel termination pulled up to 1.3 V.

50

Ω transmission lines are used with less than ± 1% tolerance on the transmission line

impedance. The transmission line lengths are as follows:

• There is a 65 mm trace length from FPGA to memory with ± 0.5 mm tolerance.

• A maximum of 1 inch tolerance is allowed to include the FPGA internal package skew

and the skew between the ball of the FPGA to the resistor pack. Package deskew is

necessary if the 1 inch tolerance is not met.

Address and Control Signals (A, BA, RASn, CASn, WEn, CSn, CKE)

For the address and control signals, no termination is required at the FPGA or DIMM.

Use 50

Ω transmission lines with less than ± 5% tolerance on the transmission line

impedance. The recommendations for the transmission line lengths are as follows:

• There must be a 65 mm trace length from FPGA to memory with ± 5 mm tolerance.

• Use a maximum of 1 inch tolerance to include the FPGA internal package skew and

the skew between the ball of the FPGA to the resistor pack. Package deskew is

necessary if the 1 inch tolerance is not met.

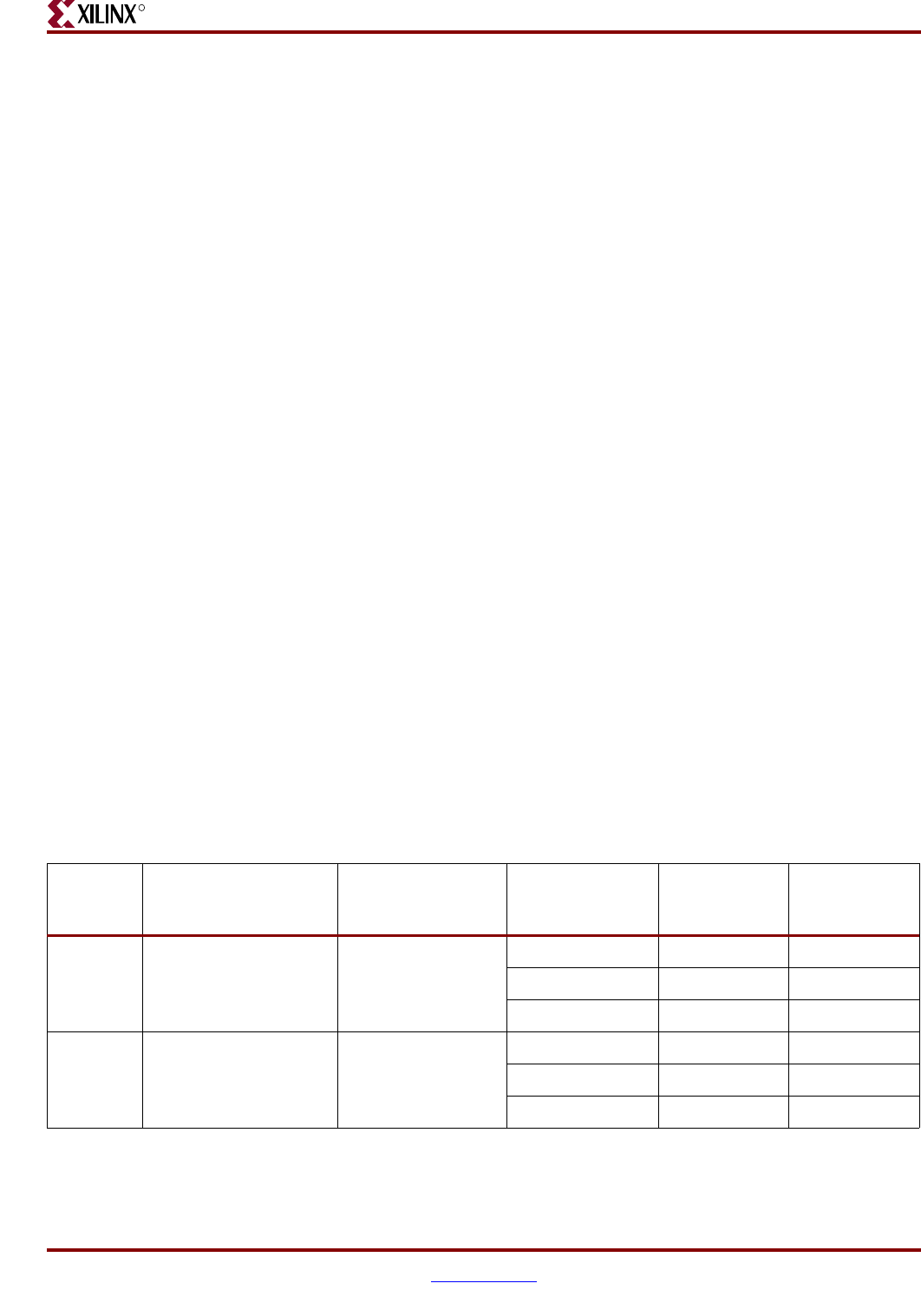

Duty Cycle Summary

Table 4-3 summarizes the duty cycle measurements taken from prelayout simulations on

50

Ω transmission lines. Refer to “IBIS Simulations,” page 29 for more simulation results.

Table 4-3: Duty Cycle Summary

No. Signal DDR Component Case

Duty Cycle

Measured at

Memory(%)

Duty Cycle

Measured at

FPGA (%)

1 Address/control Last component

(farthest from FPGA)

Typical 49.22/50.92 NA

Slow weak 49.22/50.63 NA

Fast strong 49.22/51.2 NA

2 Address/control First component

(closest to FPGA)

Typical 48.94/51.2 NA

Slow weak 49.22/51.48 NA

Fast strong 48.66/51.2 NA