52 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Chapter 4: Signal Integrity Recommendations and Simulations

R

Fast Strong Corner Case Simulation at Last DDR Component

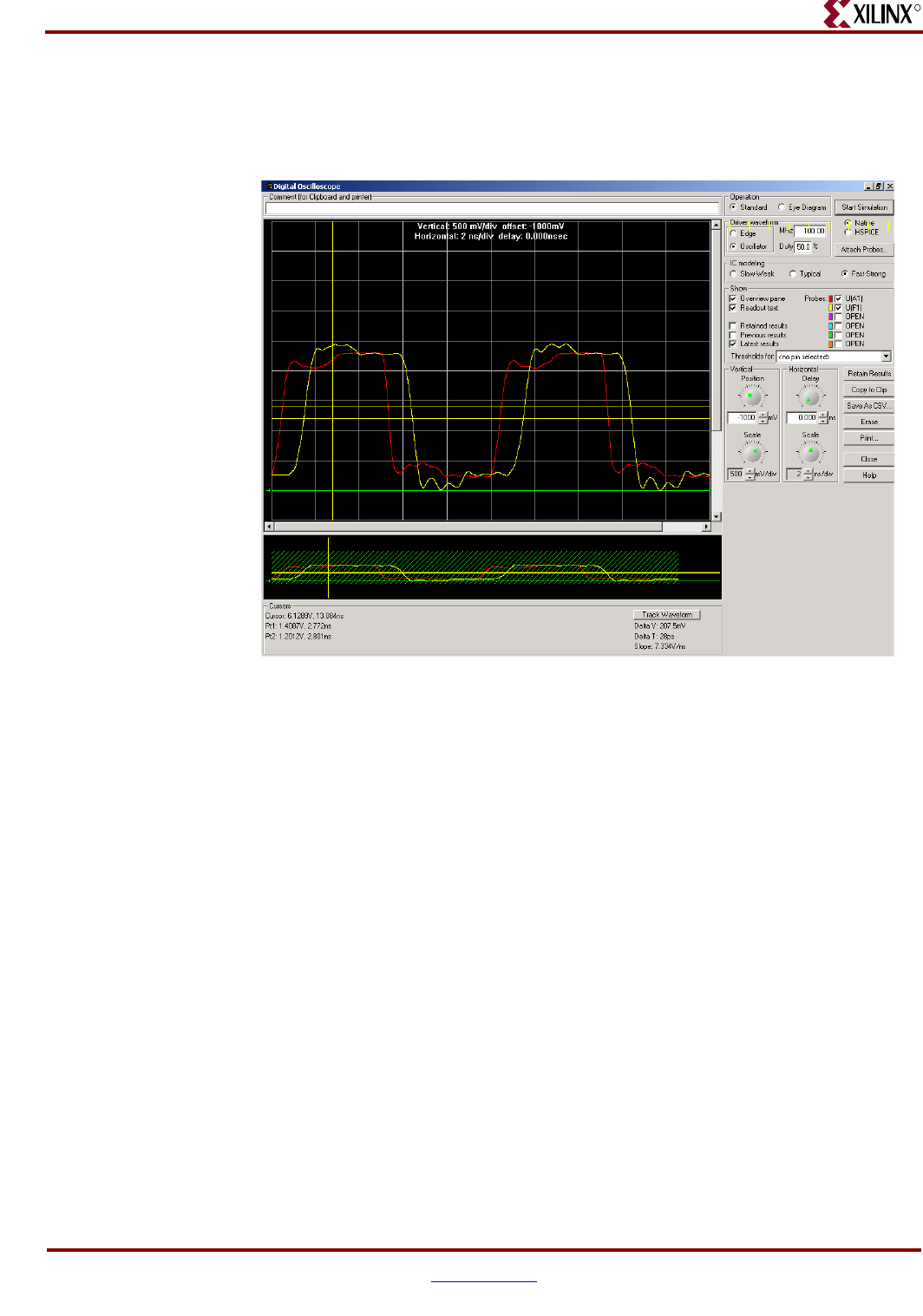

For the fast strong corner case simulation at the last DDR component, the resulting duty

cycle is 49.22/51.2. Figure 4-22 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-22

Figure 4-22: Address/Control Signals at Last DDR Memory (Fast Strong Corner

Case)

ug060_c5_21_091003