ML361 Virtex-II Pro Memory Board www.xilinx.com 31

UG060 (v1.2) November 8, 2007

IBIS Simulations

R

Data Signal Simulations

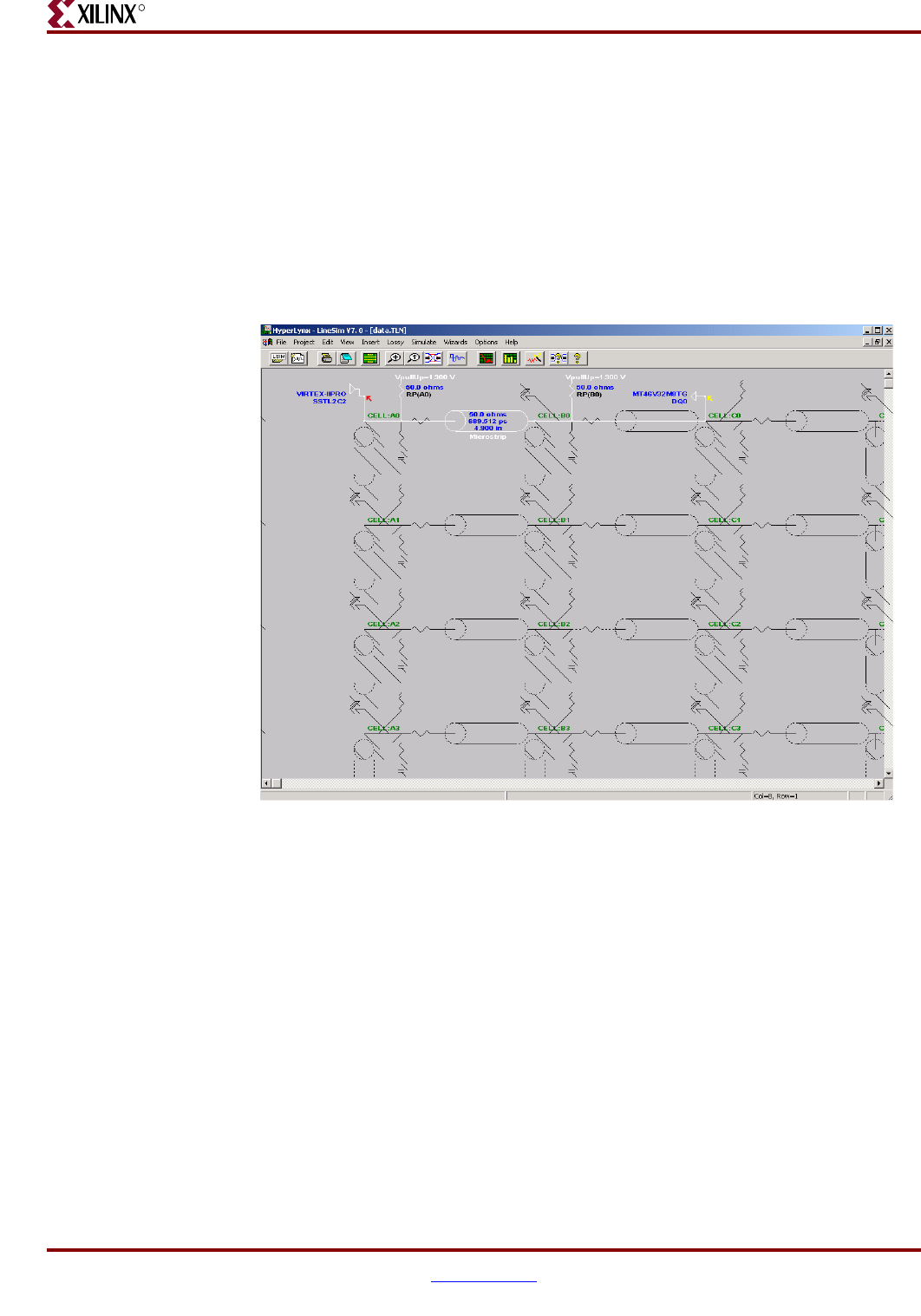

All data signal simulations below have the following test conditions for typical, slow

weak, and fast strong cases:

• Topology for data signals: 50

Ω Transmission lines

• At memory (yellow signal): 50

Ω parallel termination pulled up to 1.3 V

• At FPGA (red signal): 50

Ω parallel termination pulled up to 1.3 V (SSTL2C2 drivers at

FPGA).

Figure 4-1 shows the data signal terminations.

X-Ref Target - Figure 4-1

Figure 4-1: Data Signal Terminations

ug060_c5_01_091003