ML361 Virtex-II Pro Memory Board www.xilinx.com 23

UG060 (v1.2) November 8, 2007

FPGA Internal Power Budget

R

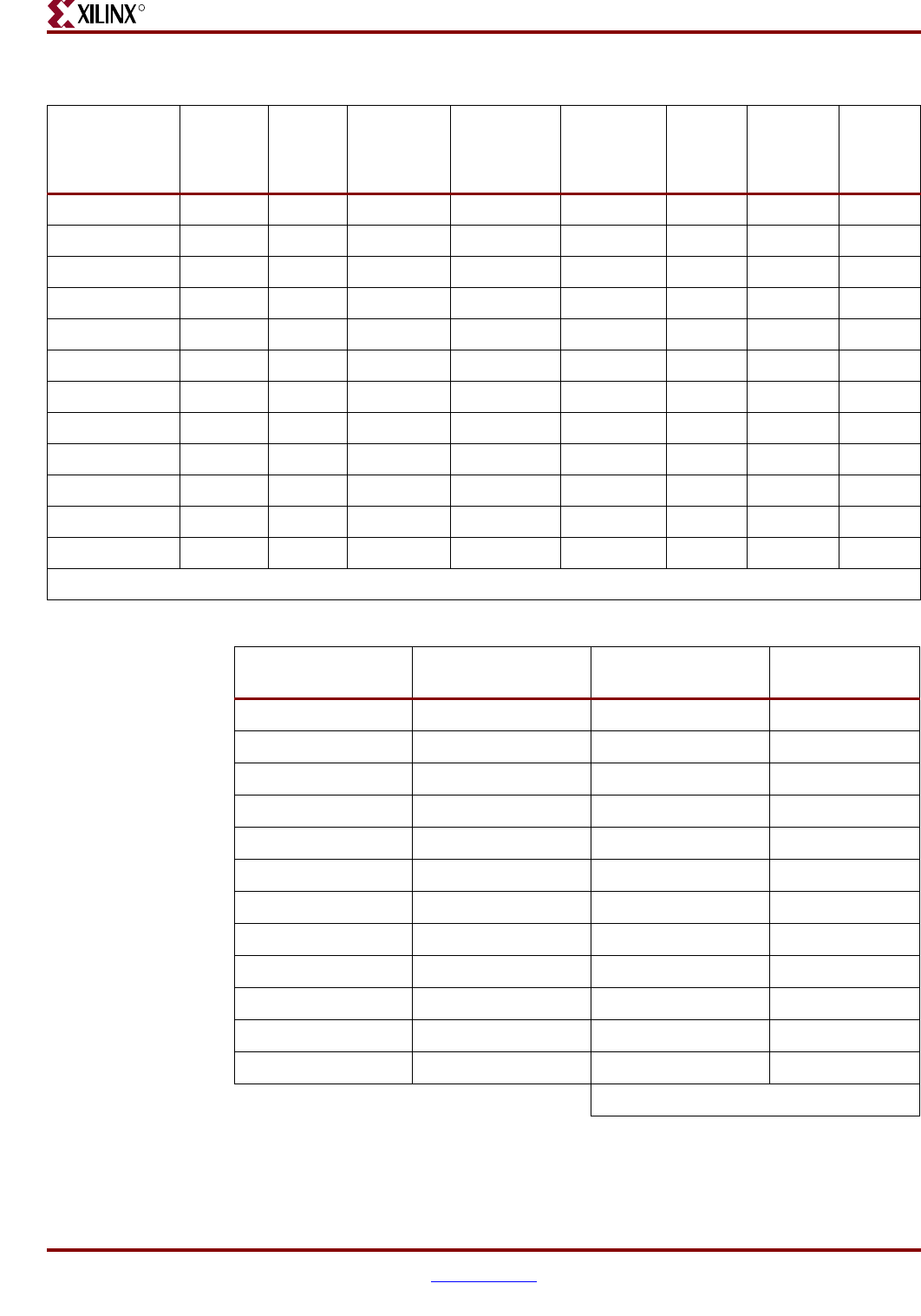

Table 3-5: CLB Logic Power

Name

Frequency

(MHz)

Total

Number

of CLB

Slices

Total

Number of

Flip/Flop or

Latches

Total Number

of Shift

Register LUTs

Total Number

of Select

RAM LUTs

Average

Toggle

Rate

%

Amount of

Routing

Used

VCC

INT

Subtotal

(mW)

User Module 1 200 2597 2603 0 1088 40% High 2439

User Module 2 0 0 0 0 0 0% Low 0

User Module 3 0 0 0 0 0 0% Low 0

User Module 4 0 0 0 0 0 0% Low 0

User Module 5 0 0 0 0 0 0% Low 0

User Module 6 0 0 0 0 0 0% Low 0

User Module 7 0 0 0 0 0 0% Low 0

User Module 8 0 0 0 0 0 0% Low 0

User Module 9 0 0 0 0 0 0% Low 0

User Module 10 0 0 0 0 0 0% Low 0

User Module 11 0 0 0 0 0 0% Low 0

User Module 12 0 0 0 0 0 0% Low 0

Total 2439

Table 3-6: Digital Clock Manager Power

Name

Clock Input

Frequency (MHz)

DCM Frequency Mode

VCC

INT

Subtotal

(mW)

User DCM 1 200 Low 6

User DCM 2 200 Low 6

User DCM 3 0 Low 0

User DCM 4 0 Low 0

User DCM 5 0 Low 0

User DCM 6 0 Low 0

User DCM 7 0 Low 0

User DCM 8 0 Low 0

User DCM 9 0 Low 0

User DCM 10 0 Low 0

User DCM 11 0 Low 0

User DCM 12 0 Low 0

Total 12