58 www.xilinx.com ML361 Virtex-II Pro Memory Board

UG060 (v1.2) November 8, 2007

Chapter 4: Signal Integrity Recommendations and Simulations

R

Data Signals from FPGA to the Last DDR Memory Component with 45Ω

Transmission Line Impedance

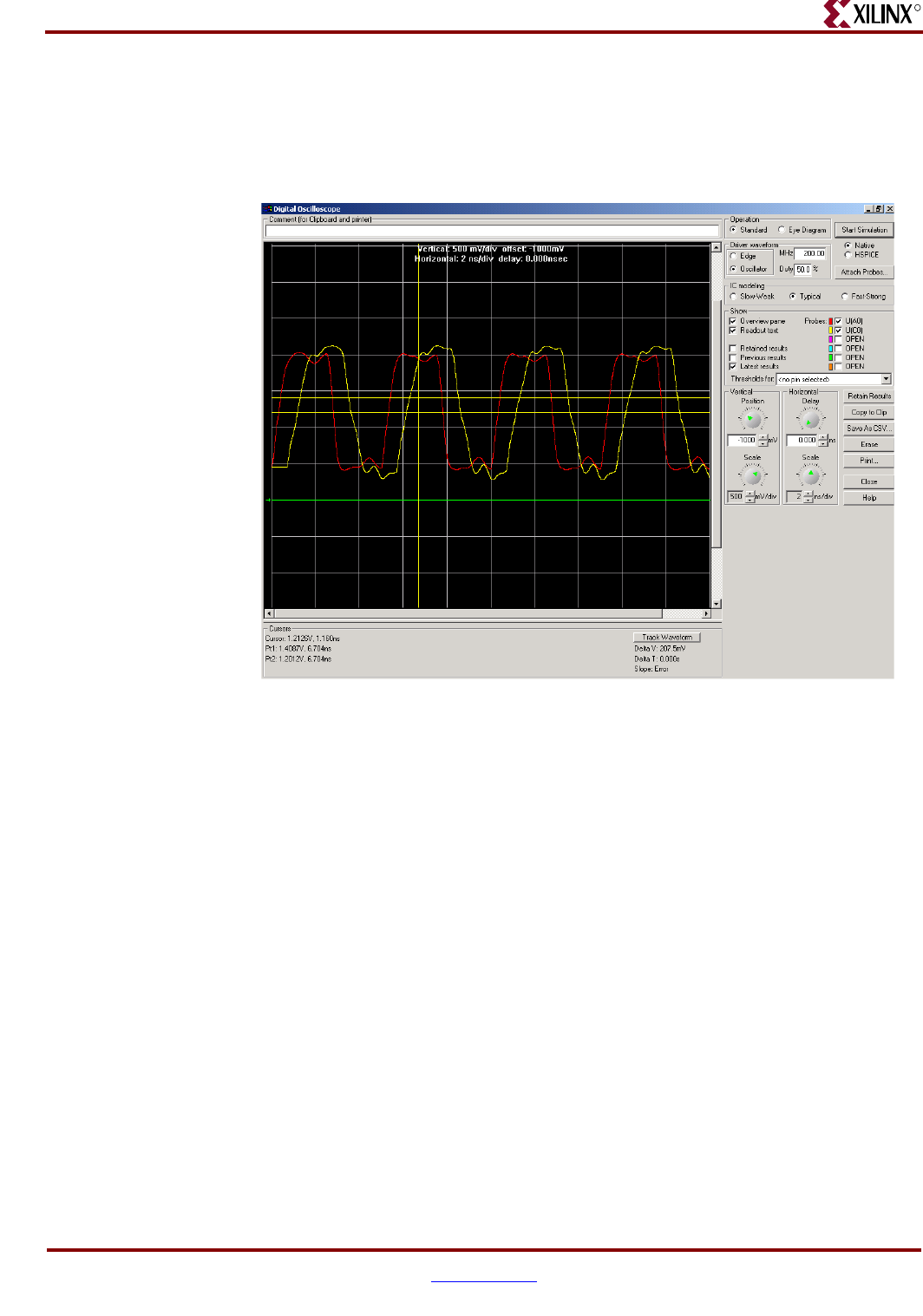

For the typical case simulation from the FPGA to the last DDR component, the resulting

duty cycle is 46.96/53.18. Figure 4-28 shows the simulation screen capture for this case.

X-Ref Target - Figure 4-28

Figure 4-28: Data Signals from FPGA to Last DDR Memory (45Ω Impedance)

ug060_c5_28_091003