ML361 Virtex-II Pro Memory Board www.xilinx.com 73

UG060 (v1.2) November 8, 2007

R

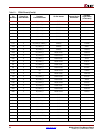

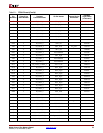

F18 0 IO_L73P_0 LED4 7223.69

E18 0 IO_L74N_0/GCLK7P GND 8692.96

D18 0 IO_L74P_0/GCLK6S GND 9819.09

J18 0 IO_L75N_0/GCLK5P GND 3858.95

H18 0 IO_L75P_0/GCLK4S GND 5131.43

H17 1 IO_L75N_1/GCLK3P CLK_200_LVDSN 5131.43

J17 1 IO_L75P_1/GCLK2S CLK_200_LVDSP 3858.95

D17 1 IO_L74N_1/GCLK1P CLK_166_LDVSN 10242.07

E17 1 IO_L74P_1/GCLK0S CLK_166_LVDSP 8752.34

F17 1 IO_L73N_1 top_clkb 7223.69

G17 1 IO_L73P_1 top_clk 5890.16

K17 1 IO_L69N_1/VREF_1 Vref = 1.3V 3320.11

L17 1 IO_L69P_1 top_dqs 2444

D16 1 IO_L68N_1 top_dq(0) 10931.46

E16 1 IO_L68P_1 top_dq(1) 9549.27

F16 1 IO_L67N_1 top_dq(2) 8063.93

G16 1 IO_L67P_1 top_dq(3) 6064.32

H16 1 IO_L57N_1/VREF_1 Vref = 1.3V 5173.85

J16 1 IO_L57P_1 top_dq(4) 3969.14

D15 1 IO_L56N_1 top_dq(5) 10275.3

D14 1 IO_L56P_1 top_dq(6) 10983.43

F15 1 IO_L55N_1 top_dq(7) 7549.54

G15 1 IO_L55P_1 top_dm 6227.05

K16 1 IO_L54N_1 top_cke 3226.4

L16 1 IO_L54P_1 top_address(0) 2263.39

C13 1 IO top_address(1) 15102.5

C14 1 IO top_address(2) 13541.32

E14 1 IO_L49N_1 top_address(3) 8634.04

F14 1 IO_L49P_1 top_address(4) 7682.05

J15 1 IO_L48N_1 top_address(5) 4150.17

K15 1 IO_L48P_1 top_address(6) 3084.88

C11 1 IO_L47N_1 top_address(7) 13513.12

D11 1 IO_L47P_1 top_address(8) 12295.94

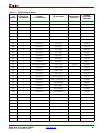

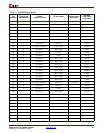

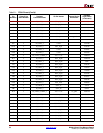

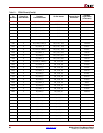

Table B-1: FPGA Pinout (Cont’d)

Pin

Numbers

Virtex-II Pro

Bank Number

Package

Functional Name

I/O Pin Names

Internal Script

Information

Package

Flight Times

(in microns)