ML361 Virtex-II Pro Memory Board www.xilinx.com 39

UG060 (v1.2) November 8, 2007

IBIS Simulations

R

Eye Diagram for Data Signal Measured at the FPGA

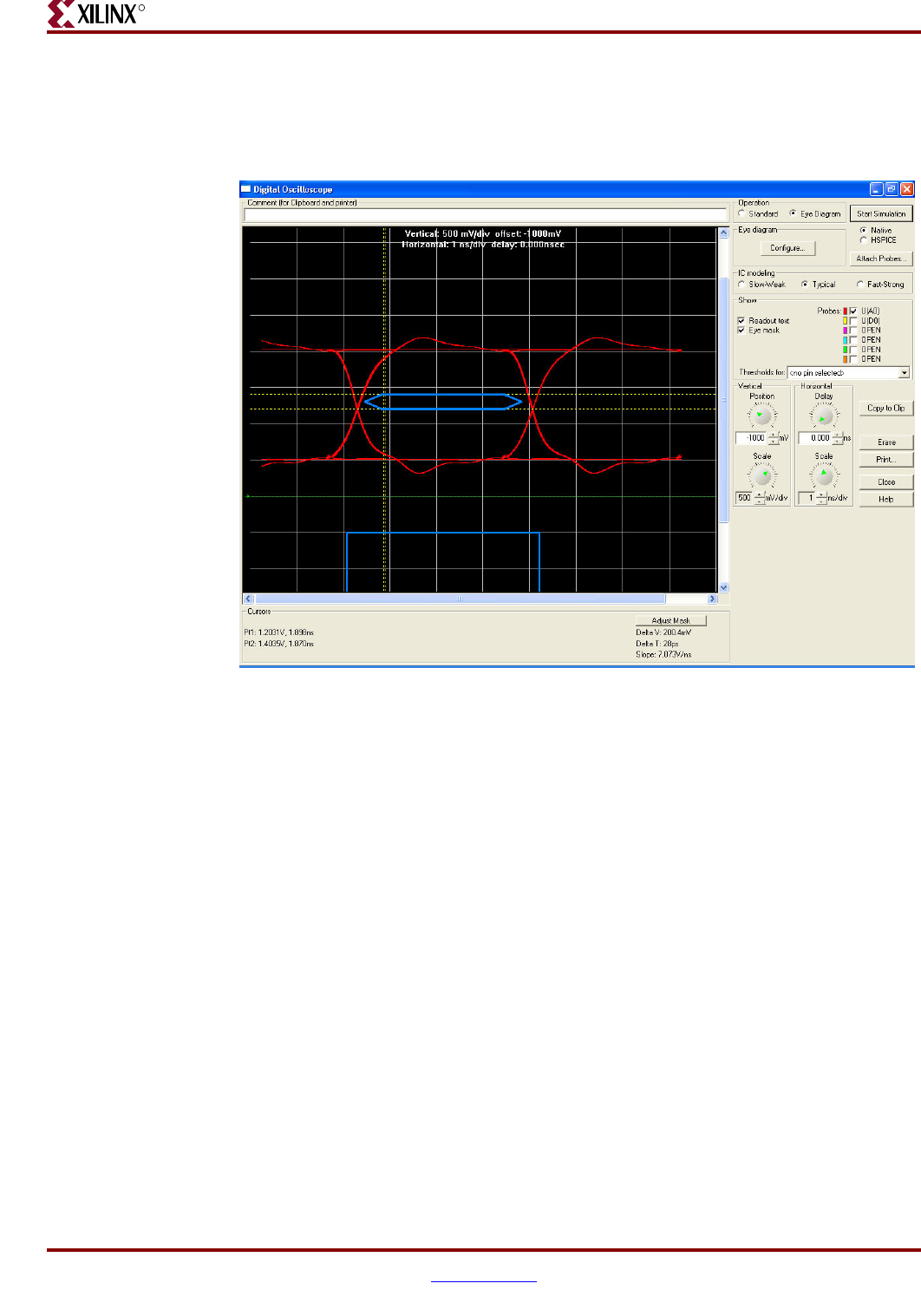

Figure 4-9 shows the eye diagram for the data signals from the FPGA to the last memory

component.

X-Ref Target - Figure 4-9

Figure 4-9: Eye Diagram for Data at the FPGA to the Last Memory Component

ug060_c5_09_031504