1–4 Alpha Architecture Handbook

1.3 Instruction Format Overview

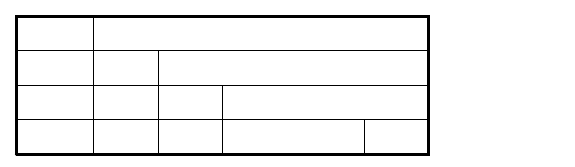

As shown in Figure 1–1, Alpha instructions are all 32 bits in length. There are four major

instruction format classes that contain 0, 1, 2, or 3 register fields. All formats have a 6-bit

opcode.

Figure 1–1: Instruction Format Overview

• PALcode instructions specify, in the function code field, one of a few dozen complex

operations to be performed.

• Conditional branch instructions test register Ra and specify a signed 21-bit PC-rela-

tive longword target displacement. Subroutine calls put the return address in register

Ra.

• Load and store instructions move bytes, words, longwords, or quadwords between

register Ra and memory, using Rb plus a signed 16-bit displacement as the memory

address.

• Operate instructions for floating-point and integer operations are both represented in

Figure 1–1 by the operate format illustration and are as follows:

– Word and byte sign-extension operators.

– Floating-point operations use Ra and Rb as source registers and write the result in

register Rc. There is an 11-bit extended opcode in the function field.

– Integer operations use Ra and Rb or an 8-bit literal as the source operand, and write

the result in register Rc.

– Integer operate instructions can use the Rb field and part of the function field to

specify an 8-bit literal. There is a 7-bit extended opcode in the function field.

1.4 Instruction Overview

PALcode Instructions

As described in Section 1.1, a Privileged Architecture Library (PALcode) is a set of subrou-

tines that is specific to a particular Alpha operating-system implementation. These subroutines

can be invoked by hardware or by software CALL_PAL instructions, which use the function

field to vector to the specified subroutine.

031 26 25 2120 1615 5 4

NumberOpcode

Opcode

Opcode

Opcode

Disp

Disp

Function RCRB

RB

RA

RA

RA

PALcode Format

Branch Format

Memory Format

Operate Format