2.3.5 PF Motor Drive Circuit

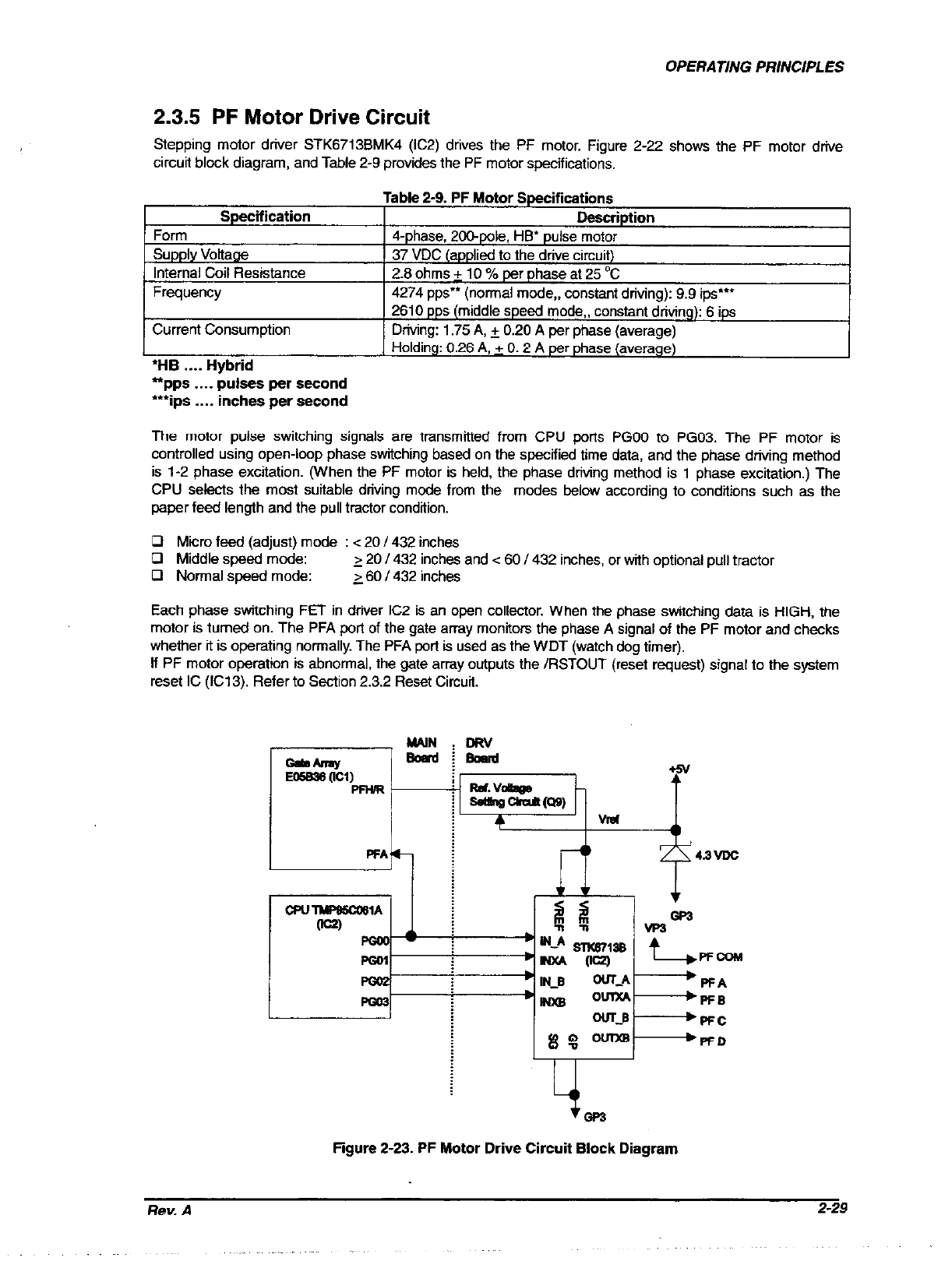

Stepping motor driver STK67138MK4 (IC2) drives the PF motor. Figure 2-22 shows the PF motor drive

circuit block diagram, and Table 2-9 provides the PF motor specifications.

Current Consumption

‘HE .._. Hybrid

“pps . . . pulses per second

“‘ips . . . inches per second

Driving: 1.75 A, + 0.20 A

The motor pulse switching signals are transmitted from CPU ports PGOO to PG03. The PF motor is

controlled using open-loop phase switching based on the specified time data, and the phase driving method

is 1-2 phase excitation. (When the PF motor is held, the phase driving method is 1 phase excitation.) The

CPU selects the most suitable driving mode from the modes below according to contiiions such as the

paper feed length and the pull tractor condition.

0 Micro feed (adjust) mode : < 20 I432 inches

Cl Middle speed mode: 2 20 I432 inches and < 60 I432 inches, or with optional pull tractor

0 Normal speed mode:

2 60 / 432 inches

Each phase switching FET in driver IC2 is an open collector. When the phase switching data is HIGH, the

motor is turned on. The PFA port of the gate array monitors the phase A signal of the PF motor and checks

whether it is operating normally. The PFA port is used as the WDT (watch dog timer).

lf PF motor operation is abnormal, the gate array outputs the /FiSTOUT (reset request) signal to the system

reset IC (IC13). Refer to Section 2.3.2 Reset Circuit.

Figure Z-23. PF Motor Drive Circuit Block Diagram

Rev. A

2-29