Chapter 4 Register Map and Descriptions

©

National Instruments Corporation 4-17 AT-MIO-16X User Manual

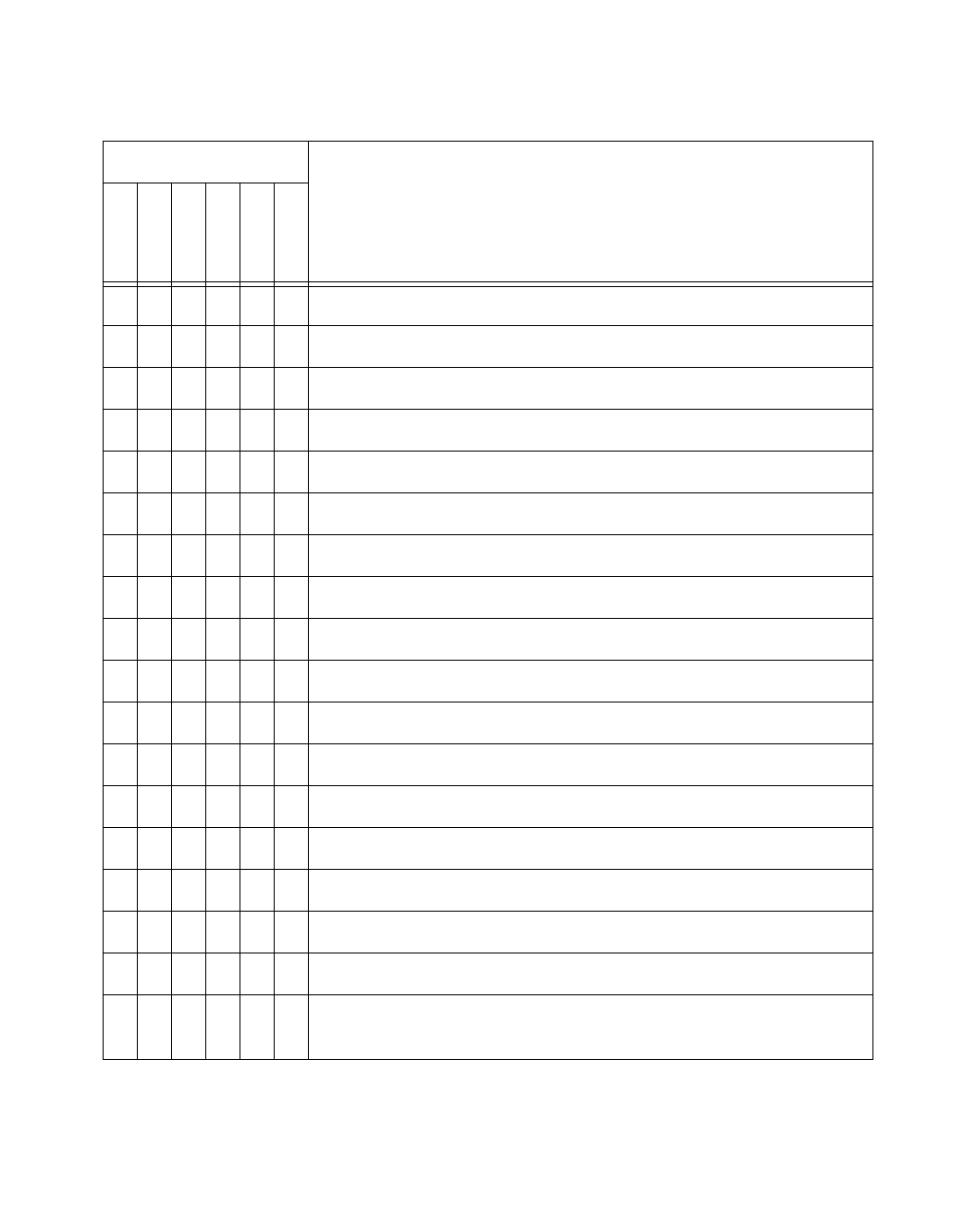

0 1 1 1 0 1 Channel A from ADC, Channel B to DAC0

0 1 1 1 1 0 Channel A from ADC, Channel B to DAC1

0 1 1 1 1 1 Channel A from ADC, Channel B to DAC0 and DAC1 (interleaved)

1 0 0 0 0 1 Timer interrupt

1 0 0 0 1 0 Timer interrupt

1 0 0 0 1 1 Timer interrupt

1 0 0 1 0 0 ADC interrupt

1 0 0 1 0 1 ADC and timer interrupt

1 0 0 1 1 0 ADC and timer interrupt

1 0 0 1 1 1 ADC and timer interrupt

1 0 0 0 0 1 Channel A to DAC0 with ADC interrupt

1 1 0 0 1 0 Channel A to DAC1 with ADC interrupt

1 1 0 0 1 1 Channel A to DAC0 and DAC1 (interleaved) with ADC interrupt

1 1 0 1 0 0 Channel A from ADC with timer interrupt

1 0 1 0 1 0 Channel B to DAC1 with ADC interrupt

1 0 1 0 1 1 Channel B to DAC0 and DAC1 (interleaved) with ADC interrupt

1 0 1 1 0 0 Channel B from ADC with timer interrupt

1 1 1 1 0 1 Channels A and B to DACs 0 and 1 (double-buffered) with ADC

interrupt

Table 4-3. DMA and Interrupt Modes (Continued)

Interface Mode

Mode Description

IO_INT

DMACHA

DMACHB

ADCREQ

DAC1REQ

DAC0REQ