Chapter 4 Register Map and Descriptions

AT-MIO-16X User Manual 4-22

©

National Instruments Corporation

update. If DACMB3 is set, the circuitry

will determine whether to perform one

read or two reads from the DAC FIFO

depending on the data in the FIFO. See

Table 4-6 for available modes and bit

patterns.

7 DACGATE DAC Update Gate—This bit controls the

update circuitry for the DACs in the

delayed update mode. If DACGATE is

set, updating of the DACs is inhibited.

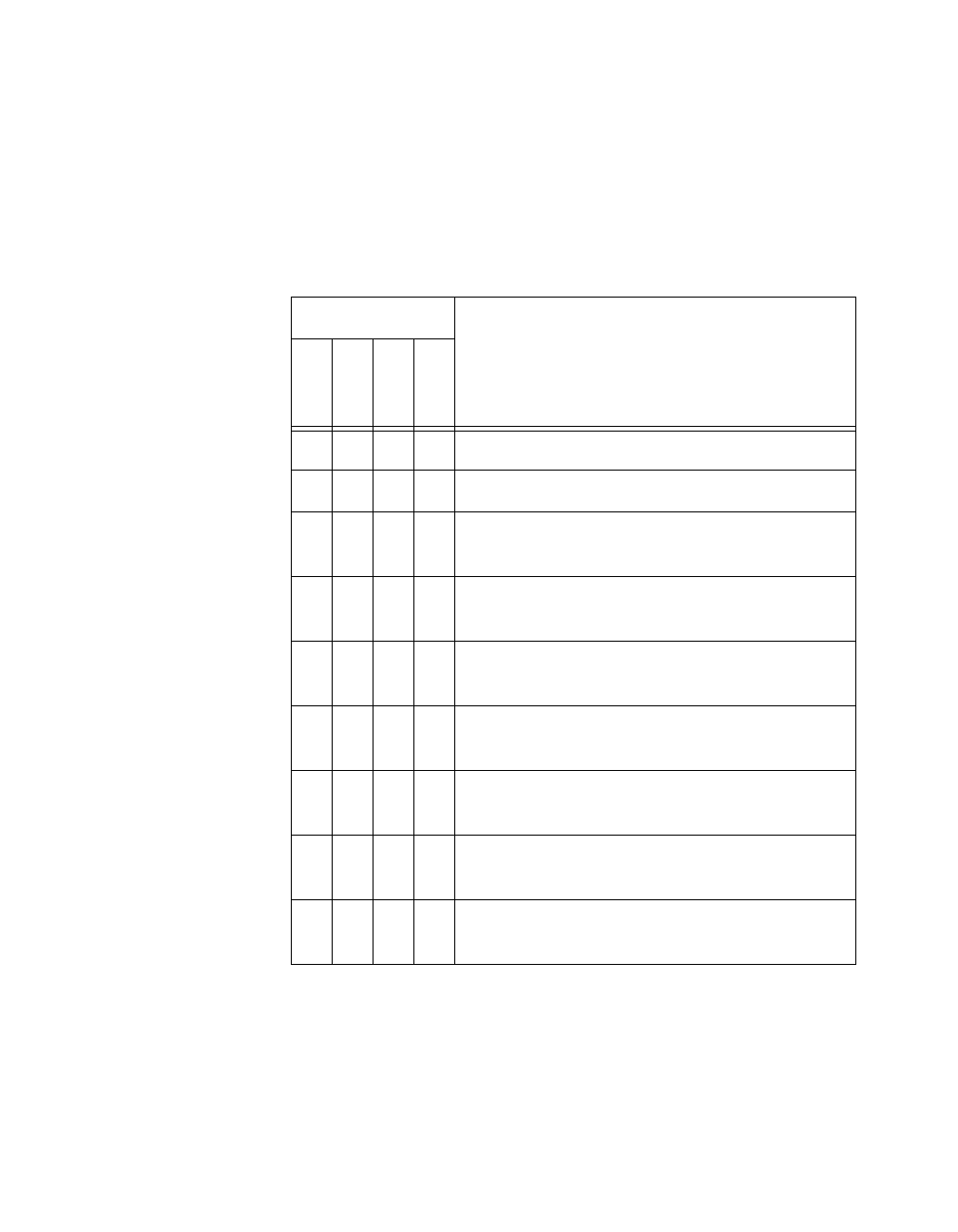

Table 4-6. Analog Output Waveform Modes

Waveform Mode

Mode Description

DACMB3

DACMB2

DACMB1

DACMB0

0 0 0 0 Single update with no timed interrupts

1 0 0 0 Single update with timed interrupts

X 0 0 1 DMA access through DAC FIFO (with single

requesting)

X 0 1 0 DMA access through DAC FIFO (with half flag

requesting)

X 0 1 1 FIFO continuous waveform generation (buffer

in DAC FIFO)

X 1 0 0 Programmed cycle waveform generation

(Counter 1 stops after N cycles)

X 1 0 1 Programmed cycle waveform generation

(Counter 2 stops after N cycles)

X 1 1 0

Programmed cycle waveform generation

(Counter 5 stops after N cycles)

X 1 1 1

Pulsed waveform (Counter 1 stops after N cycles,

Counter 2 restarts)