Chapter 4 Register Map and Descriptions

©

National Instruments Corporation 4-39 AT-MIO-16X User Manual

Writing to the channel configuration memory must be preceded with a

strobe to the CONFIGMEMCLR Register. After the channel

configuration memory is set up, the first value must be preloaded by

accessing the CONFIGMEMLD Register. Writing to the

CONFIGMEM Register following a CONFIGMEMCLR automatically

sequences into the memory list for multiple-channel configuration

values. Writing can continue until the end of the channel configuration

list is reached, or the memory becomes full. After the final write to the

channel configuration memory, the CONFIGMEMLD Register should

be strobed to load the first channel configuration value. At this point,

the channel configuration memory is primed and does not need to be

accessed again until a new channel configuration sequence is desired.

Conversions, either by EXTCONV* or by Counter 3 of the Am9513A

Counter/Timer, automatically sequence through the channel

configuration memory as programmed. When the end of the channel

configuration memory is detected, it is automatically reset to the first

value in the list. Strobing the DAQ Clear Register also resets the

channel configuration memory to the first value in the list without

destroying existing channel configuration values. A strobe of the

CONFIGMEMLD Register is still necessary to load the first value in

the memory.

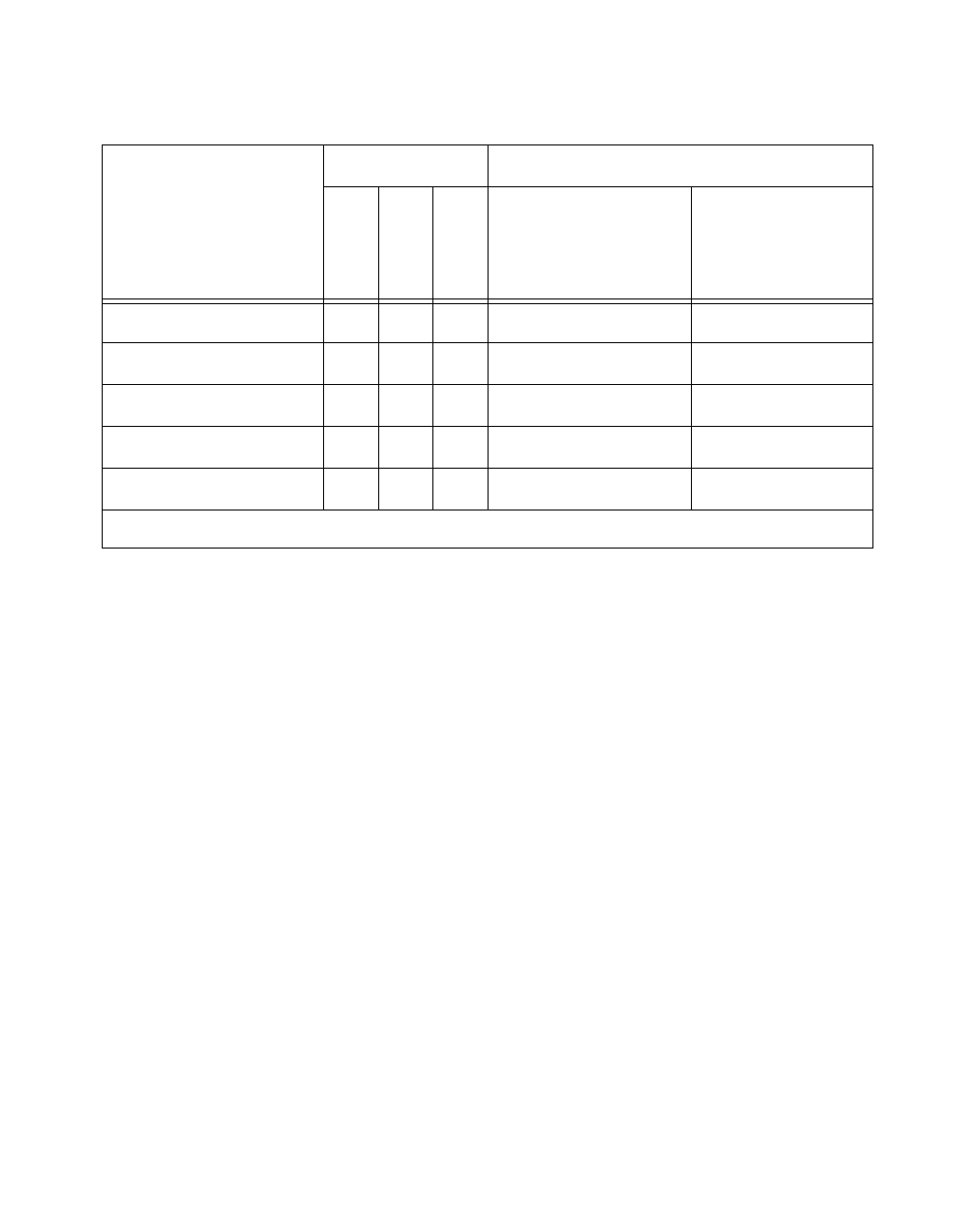

Table 4-9. Input Configuration

Input Mode

Bit Map Effect

CHAN_CAL

CHAN_SE

CHAN_AIS

PGIA (+) PGIA (–)

DIFF 0 0 X Channels 0 to 7 Channels 8 to 15

RSE 0 1 0 Channels 0 to 15 AI GND

NRSE 0 1 1 Channels 0 to 15 AI SENSE

Offset Calibration 1 X 0 AI GND AI GND

Gain Calibration 1 X 1 Internal +5 V

ref

AI GND

Note:

X indicates a

don’t care

bit.