ADCP-61-471 • Issue 4 • June 2000 • Section 2: Operation and Maintenance

2-272

© 2000, ADC Telecommunications, Inc.

TAD-104

Page 7 of 11

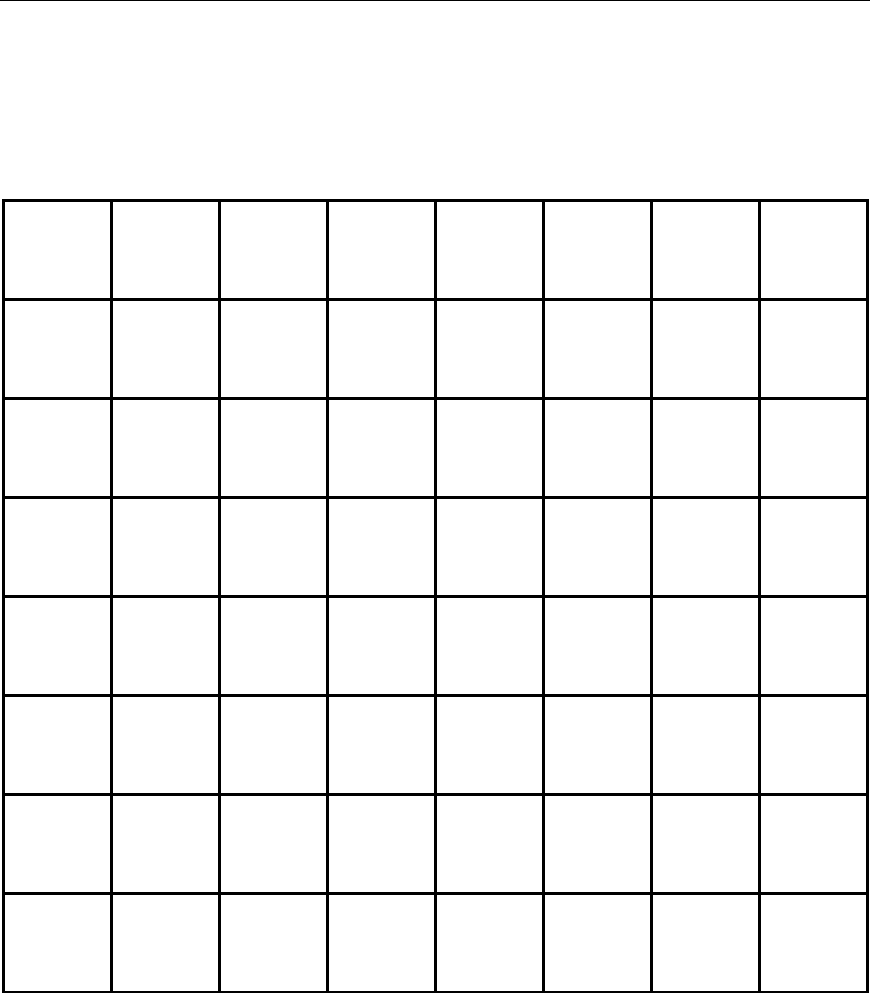

HS

EQ

HS

UNEQ

HS

IS

HS

OSS

HS

PROT

HS

UNPROT

HSW

RESET

HSP

RESET

12345678

SW TO

HSW

SW TO

HSP

HS NET

LPBK ON

HS NET

LPBK OFF

HS A NET

LPBK ON

HS A NET

LPBK OFF

HS B NET

LPBK ON

HS B NET

LPBK OFF

910111213141516

HS APS

ENAB

HS APS

DIS

HS CL

APS

LOCK

17 18 19 20 21 22 23 24

HS CUS

LPBK

ON

HS CUS

LPBK

OFF

HS A CUS

LPBK

ON

HS A CUS

LPBK

OFF

HS B CUS

LPBK

ON

HS B CUS

LPBK

OFF

25 26 27 28 29 30 31 32

MX

EQ

MX

UNEQ

MX

IS

MX

OSS

MX TX

LBO IN

MX TX

LBO OUT

MX

PROT

MX

UNPROT

33 34 35 36 37 38 39 40

SW TO

MXW

SW TO

MXP

MX NET

LPBK

ON

MX NET

LPBK

OFF

MX CUS

LPBK

ON

MX CUS

LPBK

OFF

MXW

RESET

MXP

RESET

41 42 43 44 45 46 47 48

MX APS

ENAB

MX APS

DIS

MX CL

APS

LOCK

49 50 51 52 53 54 55 56

ACO MPU

RESET

ATT

RESERVED

57 58 59 60 61 62 63 64

Note:

Bit definitions for High Speed (HS) or MUX (MX) modules are not significant when the MPU is

installed in the Soneplex Loop Extender chassis.

Figure 104-3. Command Display 1