AMD Geode™ LX Processors Data Book 115

CPU Core Register Descriptions

33234H

5.5.2.9 Instruction Fetch Configuration MSR (IF_CONFIG_MSR)

IF_CONFG_MSR controls the operation of the Instruction Fetch (IF). The Level-0 COF cache (Change of Flow (COF)

cache), L1 COF cache, return stack, and power saving mode may be turned on or off. The WRMSR instruction can access

IF_CONFIG MSR at any time. Devices external to the CPU should issue writes to IF_CONFIG MSR only if the CPU is sus-

pended or stalled.

MSR Address 00001100h

Typ e R /W

Reset Value 00000000_00005051h

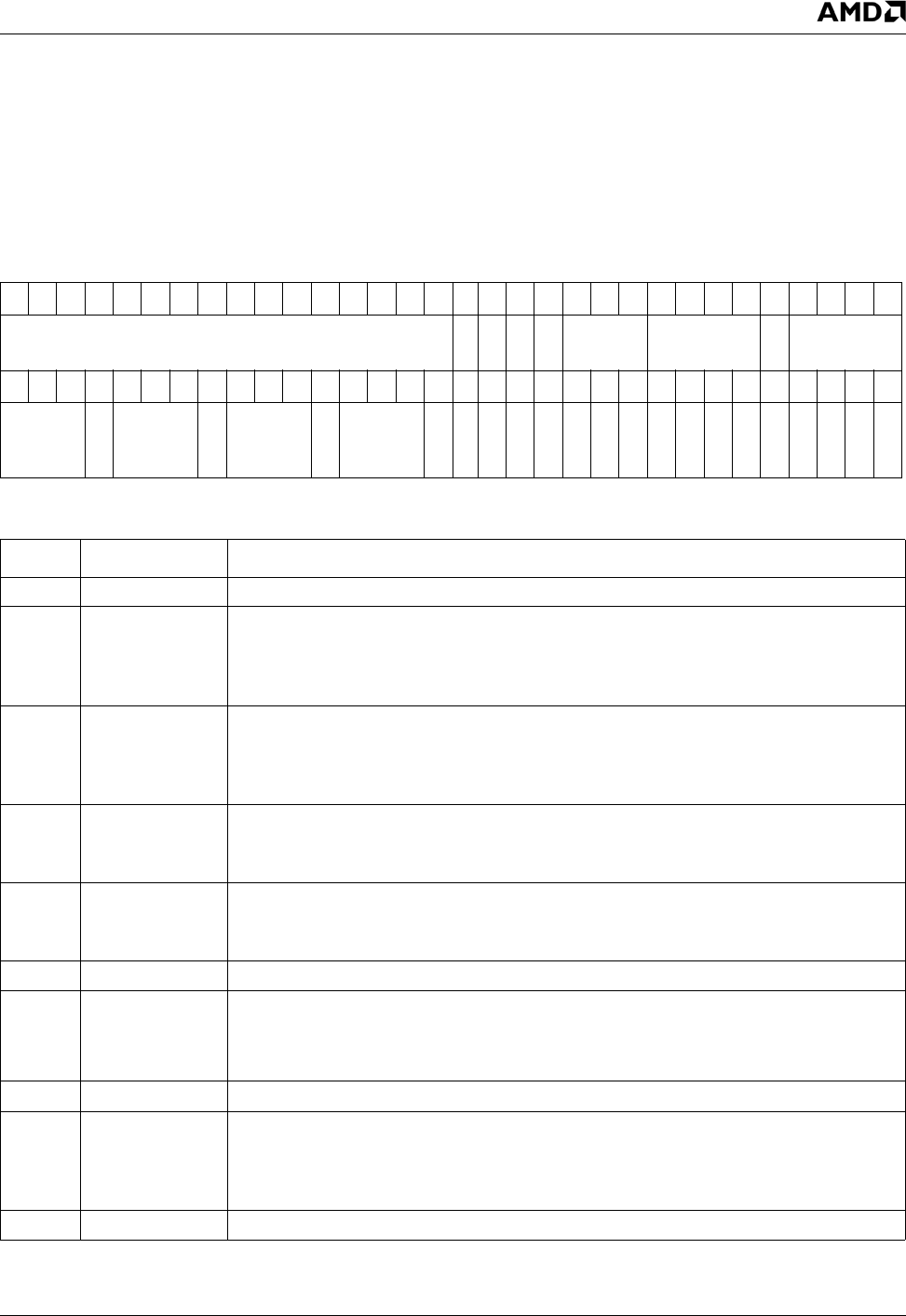

IF_CONFIG_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

BETD

BIVD

LSNPD

PSNPD

RSVD BSP

RSVD

W_DIS

313029282726252423222120191817161514131211109876543210

RSVD

II_NS

RSVD

CC_SER

RSVD

RQ_SER

RSVD

II_SER

RSVD

II_IMFLSH

RSVD

CC_L0

RSVD

DMM_DIS

RSVD

CC_PS

RSVD

STRONG

RSVD

RS

RSVD

CC_INVL

RSVD

CC_L1

IF_CONFIG_MSR Bit Descriptions

Bit Name Description

63:48 RSVD Reserved.

47 BETD Branch Tree Messaging (BTM) Exception Type. Allow the BTM stream to contain

exception type records.

0: Enable. (Default)

1: Disable.

46 BIVD Branch Tree Messaging Interrupt Vector. Allow the BTM stream to contain interrupt

vector records.

0: Enable. (Default)

1: Disable.

45 LSNPD Linear Snooping.

0: Enable. (Default)

1: Disable.

44 PSNPD Physical Snooping.

0: Enable. (Default)

1: Disable.

43:41 RSVD Reserved.

40:37 BSP Branch Tree Messaging Sync Period. Specifies the maximum period between BTM

synchronization records. If BSP is non-zero, the IF will insert a synchronization record

into the BTM stream whenever it sees a series of 32*BSP non-synchronization records.

(Default = 0)

36 RSVD Reserved.

35:32 W_DIS Branch Target Buffer (BTB) Way. Each bit is used to disable one Way of the BTB. Bit

32 = Way 0, bit 33 = Way 1, bit 34 = Way 2, and bit 35 = Way 3.

0: Enable Way. (Default)

1: Disable Way.

31:29 RSVD Reserved.