570 AMD Geode™ LX Processors Data Book

GeodeLink™ PCI Bridge

33234H

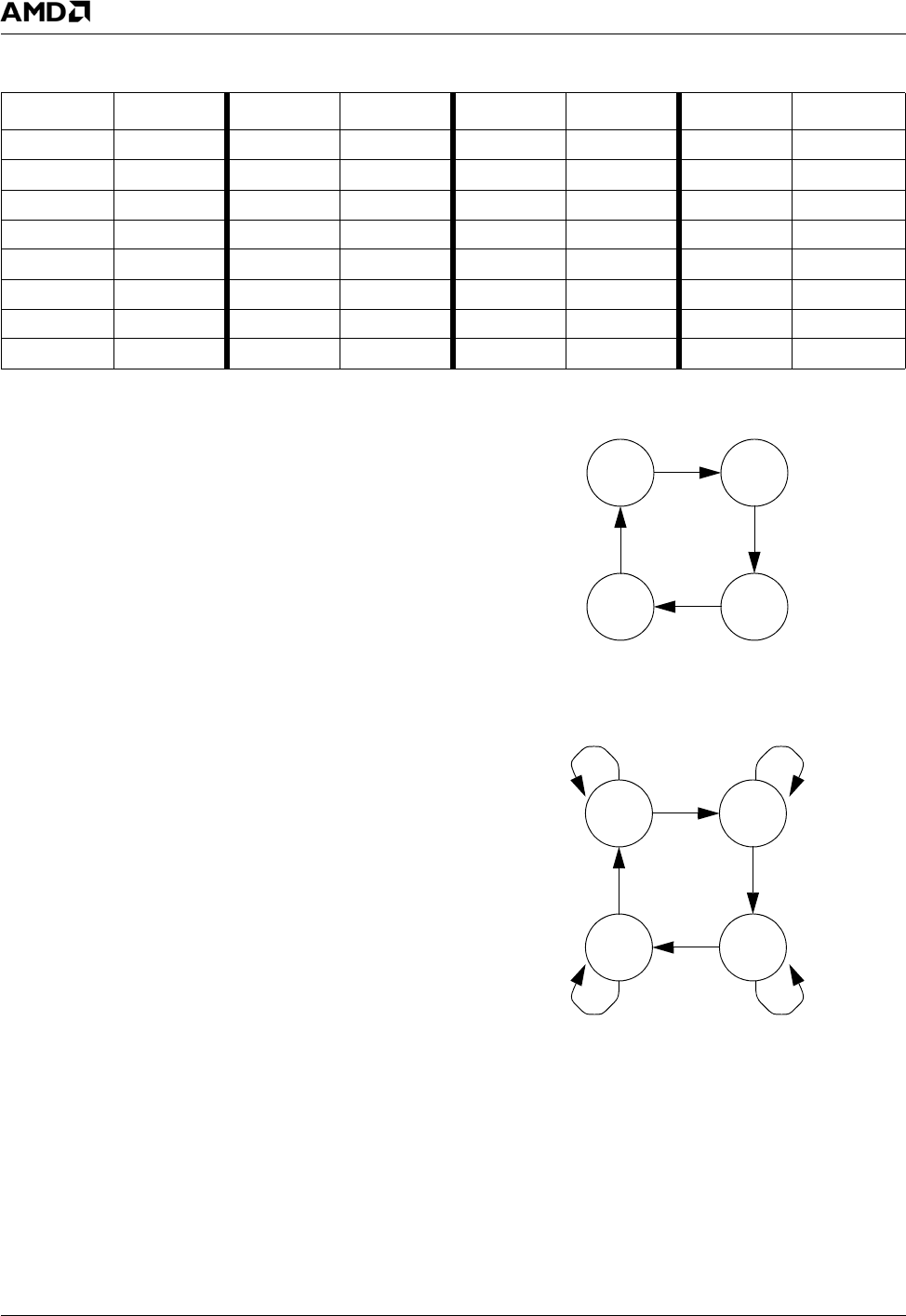

6.15.5 PCI Arbiter

The PCI arbiter implements a fair arbitration scheme with

special support for the companion device. By default it

operates as a simple round-robin arbiter that rotates prior-

ity in circular fashion (see Figure 6-60). There are three

external REQ#/GNT# pairs, numbered 0 through 2, and an

internal REQ#/GNT# pair for the CPU. REQ2#/GNT2# is

reserved for the AMD Geode companion device (i.e.,

southbridge).

Each requestor can be configured to be preemptable/non-

preemptable (Figure 6-61), given a repeat-count attribute

and given a grant-hold timeout attribute. The repeat-count

and grant-hold attributes are present to help balance the

fairness of the PCI bus when mixing bus masters of differ-

ent bursting characteristics. For example, the companion

device drops its REQ# signal after each grant and issues

relatively small bursts, while some other bus masters

present very long bursts on the PCI bus. When both bus

masters are concurrently active, the companion device

gets a very small share of the PCI bus. The repeat-count

allows a bus master to retain control of the PCI bus across

multiple bus tenures and the grant-hold keeps the grant

asserted with an idle bus for a configurable number of clock

cycles, giving the bus master a chance to reassert REQ#

again. Together they allow a small bursting bus master, like

the companion device, to repeatedly issue a sequence of

bursts before being preempted, giving it fair access to PCI

bandwidth even in the presence of a large bursting bus

master (e.g., a modern network adapter). Use of the

repeat-count attribute has an impact on the preemptability

of the bus master. That master can only be preempted

when working on its last repeated access to the bus. For

example, if a bus master has a repeat-count of 2 it may

only be preempted on its third access to the bus. The arbi-

ter can be configured to temporarily override this non-pre-

emptability, particular masters that are requesting access

to the PCI bus.

Figure 6-60. Simple Round-Robin

Figure 6-61. Weighted Round-Robin

Table 6-90. PCI Device to AD Bus Mapping

PCI Device AD Pin PCI Device AD Pin PCI Device AD Pin PCI Device AD Pin

0N/A8 18162624N/A

111919172725N/A

2 121020182826N/A

3 131121192927N/A

4 141222203028N/A

5 151323213129N/A

6 16142422N/A30N/A

7 17152523N/A31N/A

CPU 0

2 1

CPU 0

2 1