AMD Geode™ LX Processors Data Book 239

Graphics Processor

33234H

6.3.1 Command Buffer

The AMD Geode LX processor supports a command buffer

interface in addition to the normal two-deep pipelined regis-

ter interface. It is advised that software use either the com-

mand buffer interface or the register interface. It is possible

to use both, however, all pending operations should be

allowed to complete before making the switch. The com-

mand buffer interface is controlled through four registers

that specify the starting address of the command buffer,

the ending address of the command buffer, the current

write pointer and the current read pointer. The base

address (top 12 bits) of the command buffer is specified in

the GLD_MSR_CONFIG (MSR A0002001h). During initial-

ization, a block of memory is allocated to be the command

buffer space. This block must be entirely contained within a

non-cacheable 16 MB region of physical memory. The

Geode LX processor will not issue coherent transactions

for the command buffer or any other memory operations.

The starting address should be written to GP_CMD_TOP

and the ending address should be written to

GP_CMD_BOT (GP Memory Offset 50h and 54h respec-

tively). The starting address should also be written to

GP_CMD_READ (GP Memory Offset 58h). Writing to

GP_CMD_READ automatically updates GP_CMD_WRITE

(GP Memory Offset 5Ch). From this point, software can ini-

tiate an action in the processor by writing a command

buffer structure into memory at the write address

(GP_CMD_WRITE), then updating the write address to

point to the next available space in the command buffer,

either the next contiguous DWORD address, or the buffer

starting address (GP_CMD_TOP) if the wrap bit is set in

the command buffer control word. Command buffers are

allowed to wrap around the end of the command buffer

space (i.e., whenever the end of the space is reached, the

hardware will continue fetching at the beginning of the

space creating a circular buffer). However, software may

force a wrap before the end of the buffer space is reached

by setting the wrap bit in the control word, which causes

the hardware to reset its read pointer to the beginning of

the buffer space when the current command buffer is com-

plete.

Do not attempt to perform a BLT that expects host source

data for both the old source channel and channel 3 unless

one of the channels is receiving its host source data

through the command buffer, and the other is receiving it

directly from the processor. If this rule is violated, the GP

and/or the entire system may hang.

The structure of a BLT command buffer is as follows:

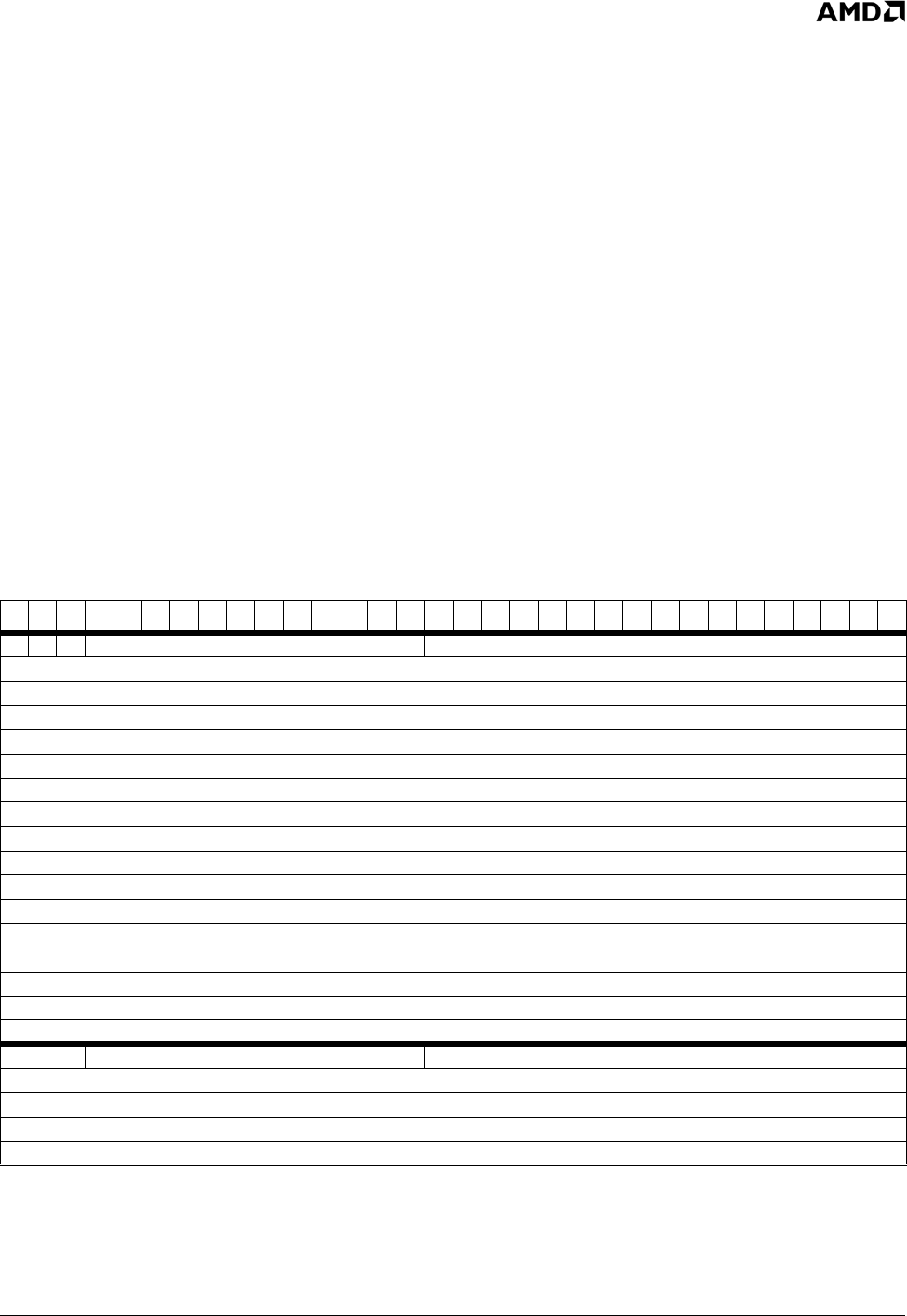

Table 6-8. BLT Command Buffer Structure

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

W 0 0 S RSVD Write Enables

GP_RASTER_MODE Data

GP_DST_OFFSET Data

GP_SRC_OFFSET Data

GP_STRIDE Data

GP_WID_HEIGHT Data

GP_SRC_COLOR_FG Data

GP_SRC_COLOR_BG Data

GP_PAT_COLOR_0 Data

GP_PAT_COLOR_1 Data

GP_PAT_DATA_0 Data

GP_PAT_DATA_1 Data

GP_CH3_OFFSET Data

GP_CH3_MODE_STR Data

GP_CH3_WIDHI Data

GP_BASE_OFFSET Data

GP_BLT_MODE Data

DTYPE RSVD DCOUNT

Optional Data Word 0

Optional Data Word 1

...

Optional Data Word n