162 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2.64 Data Memory Subsystem Configuration 1 MSR (DM_CONFIG1_MSR)

MSR Address 00001801h

Typ e R /W

Reset Value 00000000_00000000h

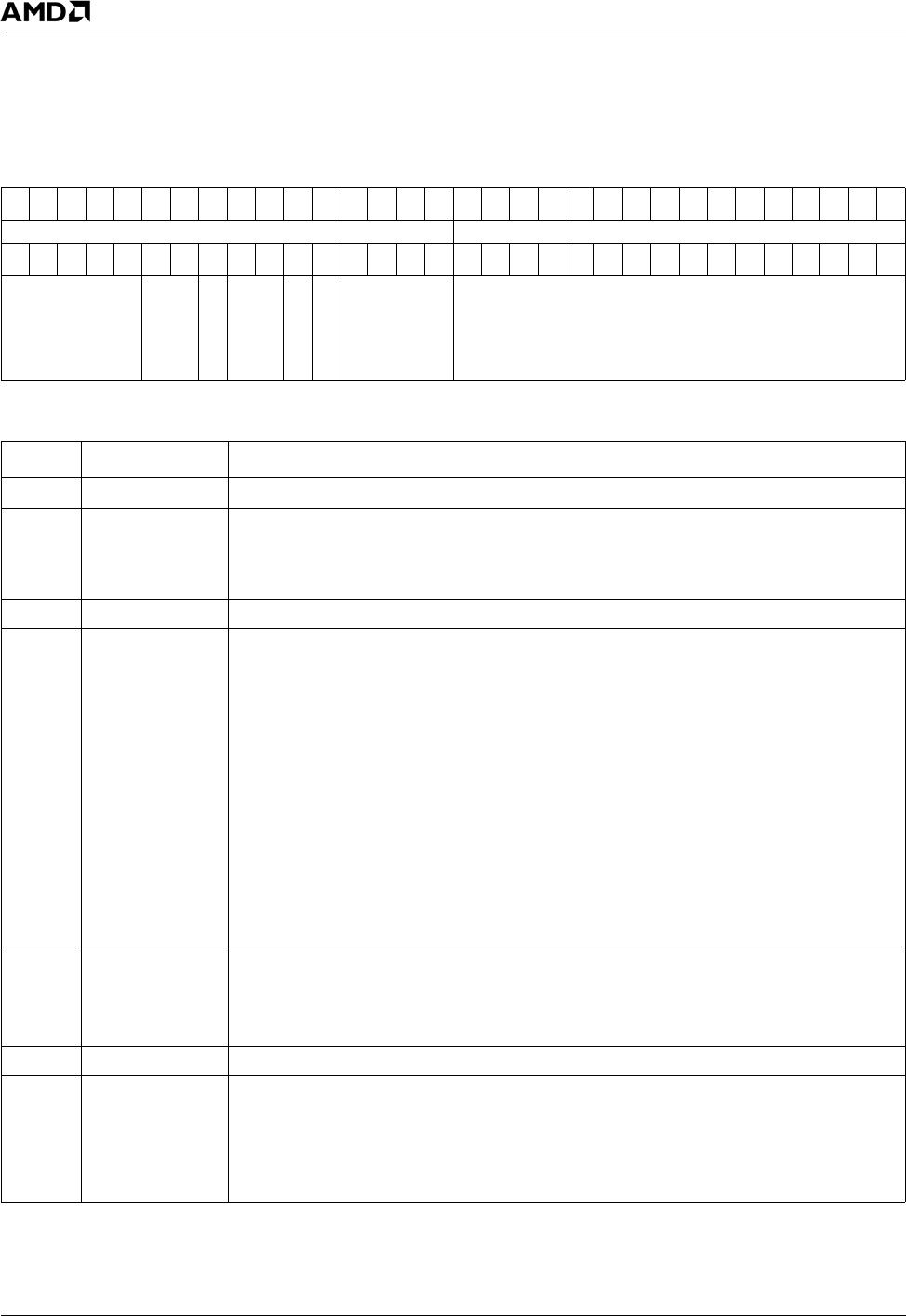

DM_CONFIG1_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD APFLOCK

313029282726252423222120191817161514131211109876543210

RSVD

APFMODE

APFENA

RSVD

PFXLOCKENA

NOPFXEVCT

ARRAYDIS PFXLOCK

DM_CONFIG1_MSR Bit Descriptions

Bits Name Description

63:48 RSVD Reserved.

47:32 APFLOCK Auto-Prefetch Lock. Bit mask of ways that cannot be allocated or replaced on an auto-

prefetch issued for a cache miss due to an instruction that is not using the restricted

cache prefix. Automatic prefetches that result from restricted cache prefix instructions

use the PFXLOCK field (bits [15:0]) for way masking. (Default = 0)

31:27 RSVD Reserved.

26:25 APFMODE Auto-Prefetch Mode. When auto-prefetching is enabled via the APFENA bit (bit 24),

APFMODE determines how the prefetches are issued as follows:

00: Even Only. An auto-prefetch is issued for the odd cache line when a fill is issued for

an even cache line, but no auto-prefetch is issued for a fill on an odd cache line. For

example, when a fill request is issued for address 0h, a prefetch will be issued for

address 20h. (Default)

01: Even/Odd. Auto-prefetches are issued for an odd cache line when an even fill is

issued, and for even cache lines when an odd fill is issued. (i.e the auto-prefetch

address is the toggle of fill address A[5]). Using this mode effectively increases the

DM logical cache line size to 64 bytes for fills. Line replacements and snoop evictions

are still done using a 32-byte line size.

1x: Increment. Auto-prefetches are issued for the next cache line (auto-prefetch line = fill

line + 1) when a fill is issued, except for the last cache line in a 4K page (fill address

bits [11:5] = 1111111b).

24 APFENA Auto-Prefetch Enable. Allows DM to perform automatic prefetch operations based on

cache fills as specified by the APFMODE field (bits [26:25]).

0: Disable.

1: Enable.

23:22 RSVD Reserved.

21 PFXLOCKENA Prefetch Prefix Instructions Lock Enable. When this bit is enabled, the LSLOCK field

in DM_CONFIG0 (MSR 00001800h[31:16]) determines which ways are available for

replacement for all processor memory references except prefetch instructions.

0: Disable the restricted cache feature. (Default)

1: Enable the restricted cache feature (PFXLOCK field, bits [15:0]).