82 AMD Geode™ LX Processors Data Book

GLIU Register Descriptions

33234H

4.2.4.3 P2D Range Descriptor (P2D_R)

See Table 4.1.3.1 "Memory Routing and Translation" on page 47 for details on the descriptor usage.

GLIU0 P2D_R[0]

MSR Address 10000028h

Typ e R /W

Reset Value 00000000_000FFFFFh

GLIU1 P2D_R[3:0]

MSR Address 4000002Ah-4000002Dh

Type R /W

Reset Value 00000000_000FFFFFh

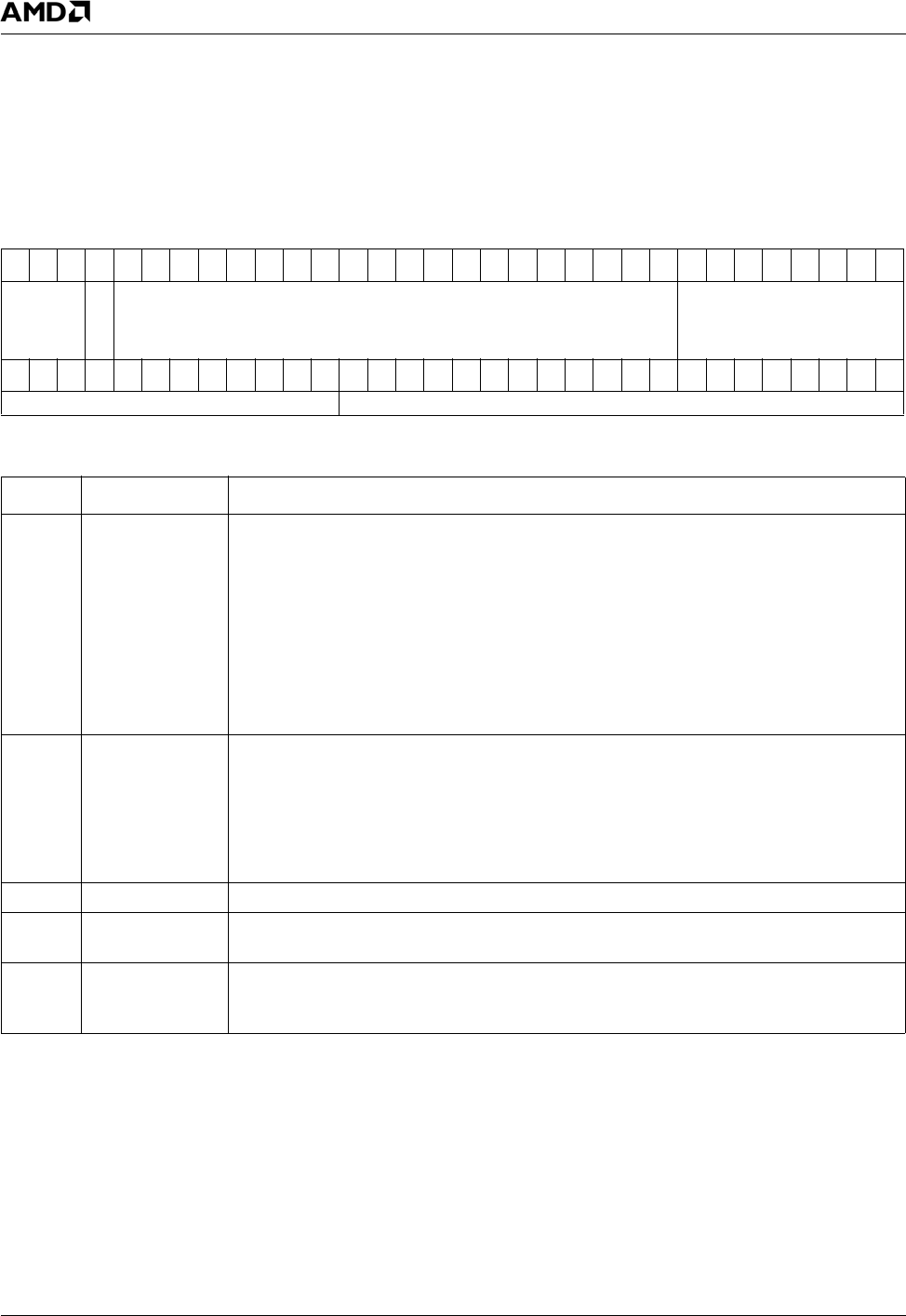

P2D_R Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

PDID1

PCMP_BIZ

RSVD PMAX

313029282726252423222120191817161514131211109876543210

PMAX PMIN

P2D_R Bit Descriptions

Bit Name Description

63:61 PDID1 Descriptor Destination ID. These bits define which Port to route the request to, if it is a

‘hit’ based on the other settings in this register.

000: Port 0 (GLIU0 = GLIU; GLIU1 = GLIU.)

001: Port 1 (GLIU0 = GLMC; GLIU1 = Interface to GLIU0.)

010: Port 2 (GLIU0 = Interface to GLIU1; GLIU1 = VP.)

011: Port 3 (GLIU0 = CPU Core; GLIU1 = GLCP.)

100: Port 4 (GLIU0 = DC; GLIU1 = GLPCI.)

101: Port 5 (GLIU0 = GP; GLIU1 = VIP.)

110: Port 6 (GLIU0 = Not Used; GLIU1 = SB.)

111: Port 7 (GLIU0 = Not Used; GLIU1 = Not Used.)

60 PCMP_BIZ Compare Bizzaro Flag.

0: Consider only transactions whose Bizzaro flag is low as a potentially valid address hit.

A low Bizzaro flag indicates a normal transaction cycle such as a memory or I/O.

1: Consider only transactions whose Bizzaro flag is high as a potentially valid address

hit. A high Bizzaro flag indicates a ‘special’ transaction, such as a PCI Shutdown or

Halt cycle.

59:40 RSVD Reserved.

39:20 PMAX Physical Memory Address Max. These bits form the value denoting the upper (ending)

address of the physical memory, which is compared to determine a hit.

19:0 PMIN Physical Memory Address Min. These bits form the value denoting the lower (starting)

address of the physical memory, which is compared to determine a hit. Hence, a hit

occurs if the physical address [31:12] >= PMIN and <= PMAX.