158 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2.61 Instruction Memory Subsystem BIST Tag MSR (IM_BIST_TAG_MSR)

The Instruction Memory subsystem supports built-in self-test (BIST) for the tag and data arrays. Normally, BIST is run dur-

ing manufacturing test. For convenience, BIST can be activated by reading the BIST MSRs.

WARNING: It is important that the instruction cache be disabled before initiating BIST via MSRs. There are no guarantees

of proper behavior if BIST is activated with the instruction cache enabled. The instruction cache can be disabled through

the IM_CONFIG_MSR (MSR 00001700h[4]).

5.5.2.62 Instruction Memory Subsystem BIST Data MSR (IM_BIST_DATA_MSR)

MSR Address 00001730h

Typ e RO

Reset Value 00000000_0000000xh

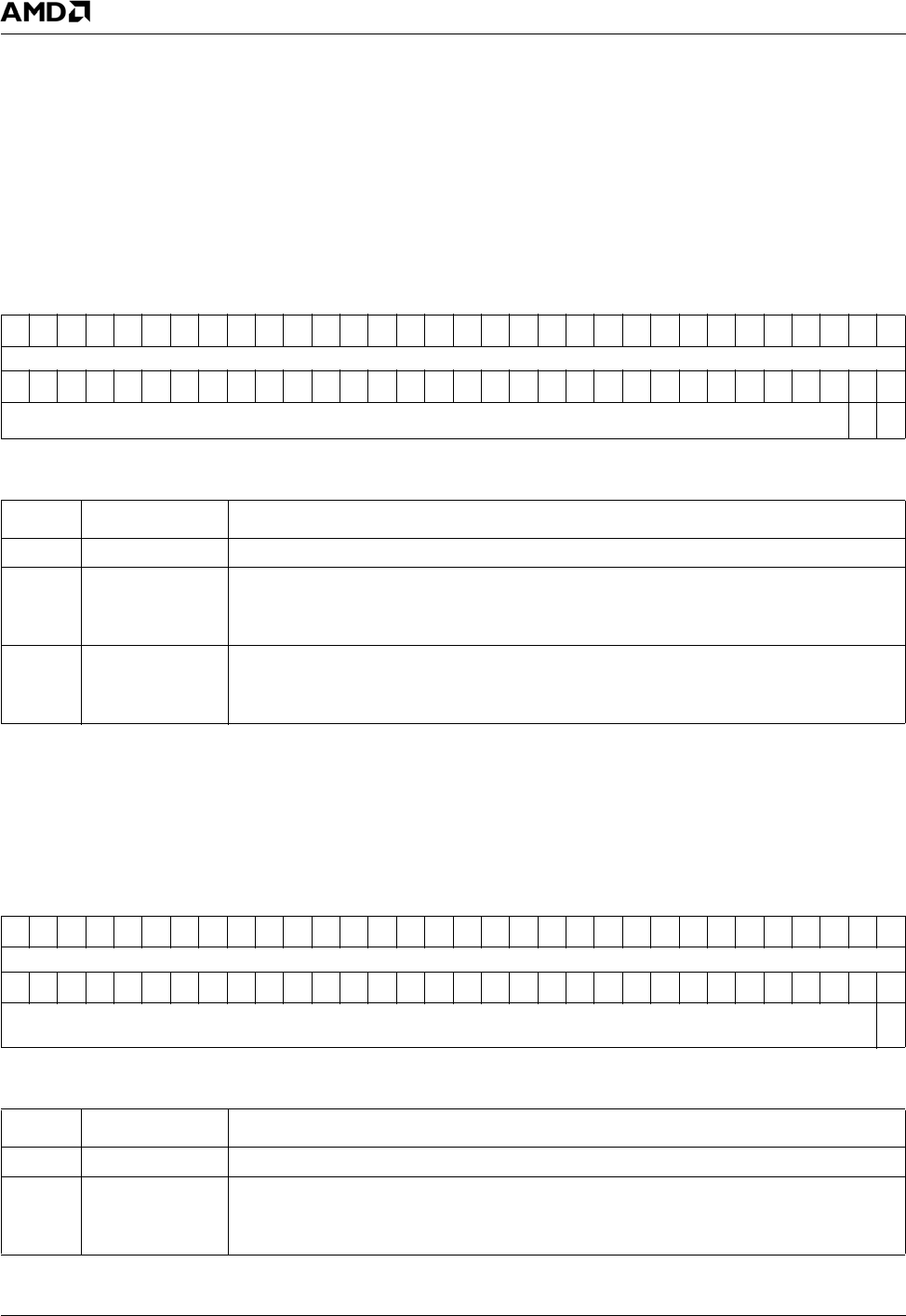

IM_BIST_TAG_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

CMP

TAG

IM_BIST_TAG_MSR Bit Descriptions

Bits Name Description

63:2 RSVD (RO) Reserved (Read Only). (Default = 0)

1CMP Tag Compare Logic BIST.

0: Fail (Default)

1: Pass

0TAG Valid and Tag Array BIST.

0: Fail (Default)

1: Pass

MSR Address 00001731h

Typ e RO

Reset Value 00000000_0000000xh

IM_BIST_DATA_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

DATA

IM_BIST_DATA_MSR Bit Descriptions

Bits Name Description

63:1 RSVD (RO) Reserved (Read Only). (Default = 0)

0DATA Data Array BIST.

0: Fail

1: Pass