504 AMD Geode™ LX Processors Data Book

Video Input Port Register Descriptions

33234H

6.10.2.21 VIP Task B U Offset (VIP_TASK_B_U_OFFSET)

6.10.2.22 VIP Ancillary Data/Message Passing/Data Streaming Buffer1 Base Address (VIP_ANC_MSG_1_BASE)

VIP Memory Offset 54h

Typ e R /W

Reset Value 00000000h

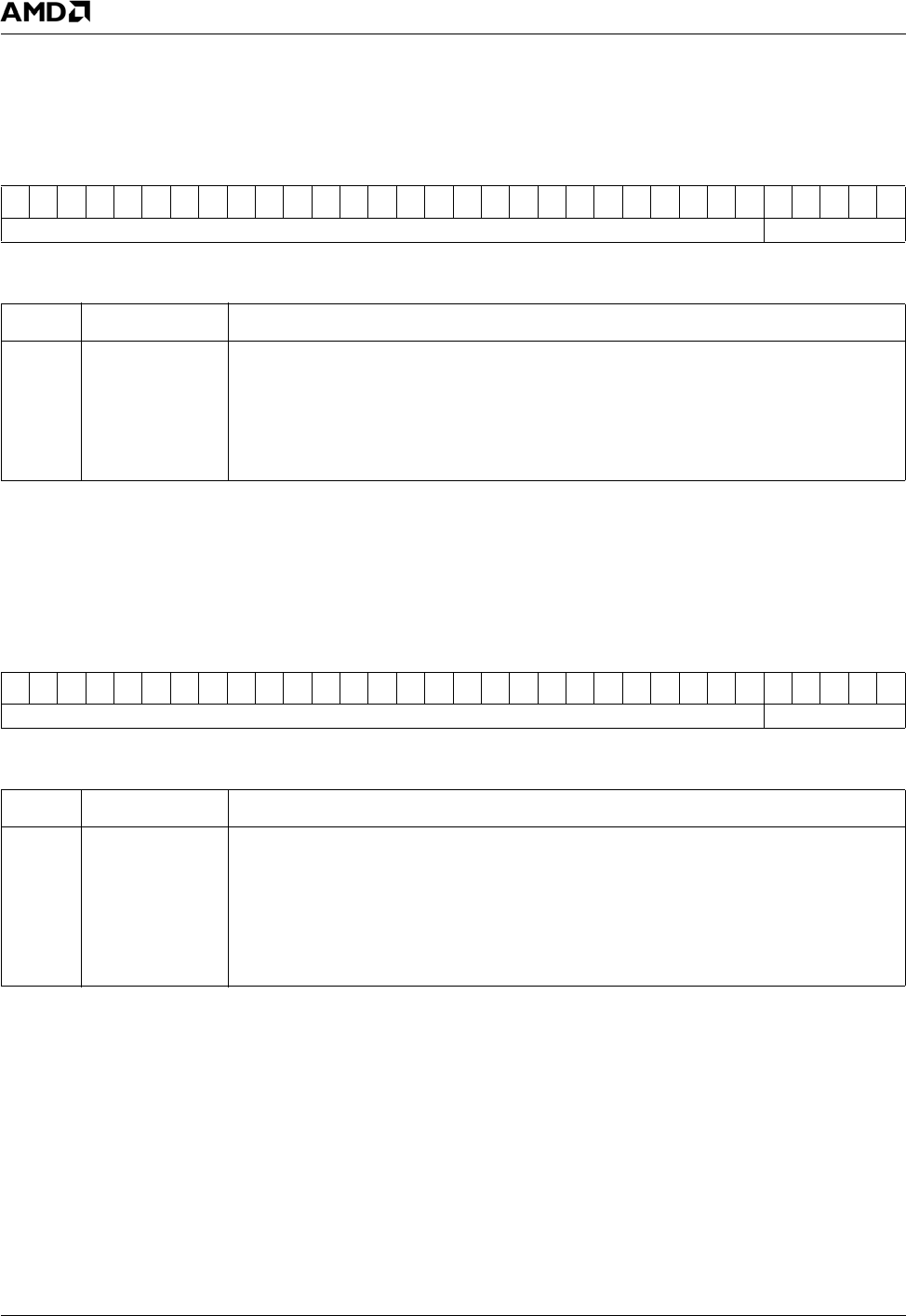

VIP_TASK_B_U_OFFSET Register Map

313029282726252423222120191817161514131211109876543210

TASK_B_U_OFFSET Program to 00000

VIP_TASK_B_U_OFFSET Bit Descriptions

Bit Name Description

31:0 TASK_B_U_

OFFSET

Task B U Offset. This register determines the starting address of the U buffer when data

is stored in planar format. The start of the U buffer is determined by adding the contents

of this register to that of the base address. The value in this register must be 32-byte

aligned. (Bits [4:0] are required to be 00000.)

Note: This register in NOT double buffered and should be initialized before start of

video capture.

VIP Memory Offset 58h

Typ e R /W

Reset Value 00000000h

VIP_ANC_MSG_1_BASE Register Map

313029282726252423222120191817161514131211109876543210

ANC_MSG_1_BASE Program to 00000

VIP_ANC_MSG_1_BASE Bit Descriptions

Bit Name Description

31:0 ANC_MSG_1_

BASE

Ancillary Data/Message Passing Data/Data Streaming Base Address. This register

specifies the base address for the ancillary data when in VIP modes or message/stream-

ing data when in Message Passing or Data Streaming modes. Changes to this register

take effect at the beginning of the next field when in VIP mode. It takes place immediately

when in Message Passing or Data Streaming mode. The value in this register must be

32-byte aligned. (Bits [4:0] are required to be 00000.)

Note: This register is NOT double buffered.