AMD Geode™ LX Processors Data Book 505

Video Input Port Register Descriptions

33234H

6.10.2.23 VIP Ancillary Data/Message Passing/Data Streaming Buffer 2 Base Address (VIP_ANC_MSG_2_BASE)

6.10.2.24 VIP Ancillary Data/Message Passing/Data Streaming Buffer Size (VIP_ANC_MSG_SIZE)

VIP Memory Offset 5Ch

Typ e R /W

Reset Value 00000000h

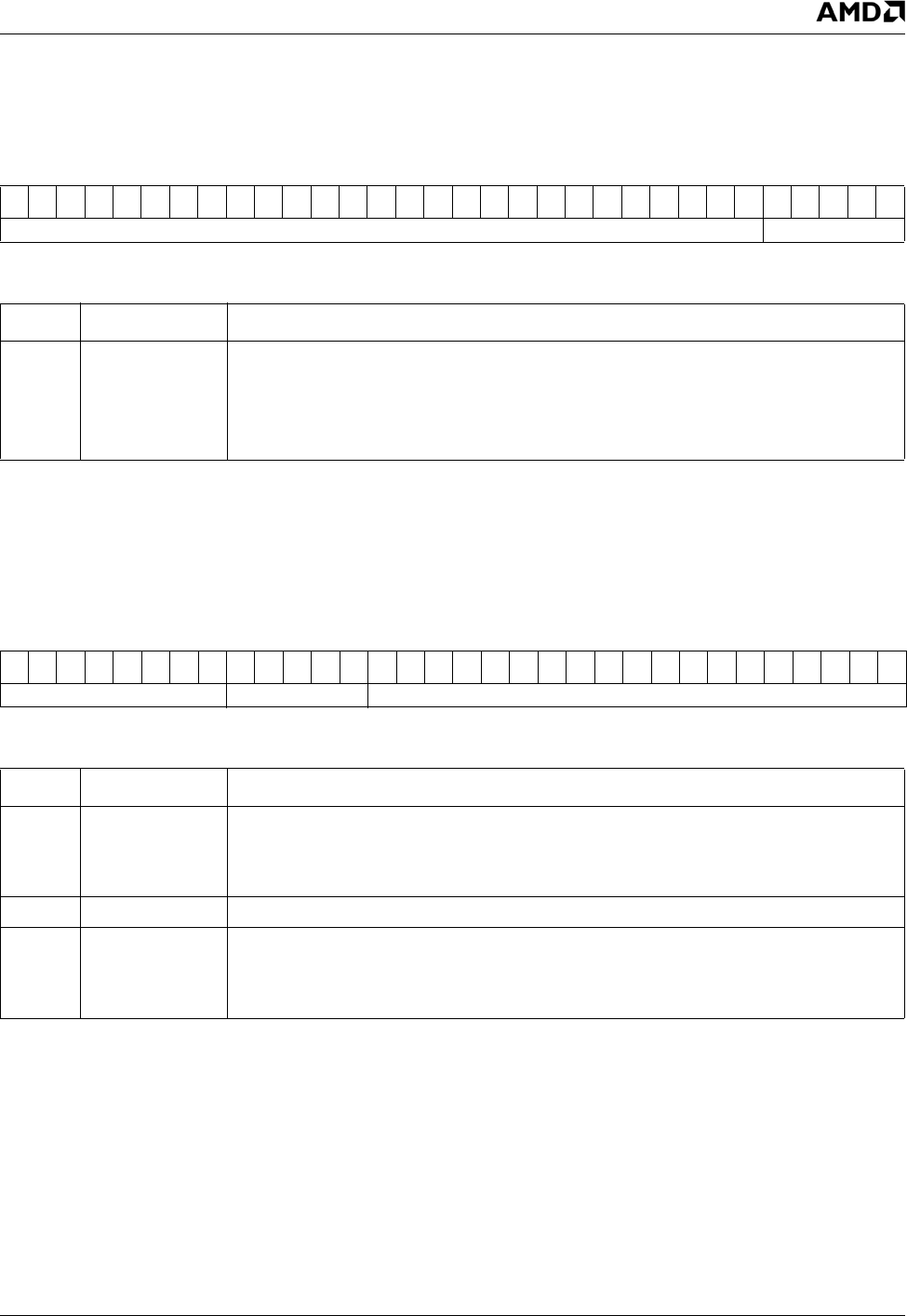

VIP_ANC_MSG_2_BASE Register Map

313029282726252423222120191817161514131211109876543210

ANC_MSG_2_BASE Program to 00000

VIP_ANC_MSG_2_BASE Bit Descriptions

Bit Name Description

31:0 ANC_MSG_2_

BASE

Message Passing Data/Data Streaming Base Address. This register specifies the

base address for the second buffer used in Message Passing and Data Streaming

modes. Data written to this register takes place immediately (no double buffer). The

value in this register must be 32-byte aligned. (Bits [4:0] are required to be 00000.)

Note: This register is NOT double buffered.

VIP Memory Offset 60h

Typ e R /W

Reset Value 00000000h

VIP_ANC_MSG_SIZE Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ANC_PACK_INT_THRESH RSVD ANC_MSG_STREAM_SIZE

VIP_ANC_MSG_SIZE Bit Descriptions

Bit Name Description

31:24 ANC_PACK_

INT_THRESH

Ancillary Packet Interrupt Threshold Value. This value determines when the ancillary

interrupt occurs. The Ancillary Packet Count (APC) bits (VIP Memory Offset 08h[31:24])

is compared to this value. If the APC is equal to or greater then this value, the ancillary

interrupt is generated.

23:19 RSVD Reserved.

18:0 ANC_MSG_

STREAM_SIZE

Ancillary Data/Message Passing Data/Data Streaming Buffer Size. This register

specifies the size of the ancillary, message passing, and data streaming buffers in bytes.

Changes to this register take effect immediately (not double buffered). The value in this

register is 8-byte aligned. Bits [2:0] are ignored.