AMD Geode™ LX Processors Data Book 539

GeodeLink™ Control Processor Register Descriptions

33234H

6.14 GeodeLink™ Control Processor Register Descriptions

All GeodeLink Control Processor registers are Model Spe-

cific Registers (MSRs) and are accessed via the RDMSR

and WRMSR instructions.

The registers associated with the GLCP are the Standard

GeodeLink™ Device (GLD) MSRs and GLCP Specific

MSRs. Table 6-85 and Table 6-86 are register summary

tables that include reset values and page references where

the bit descriptions are provided.

Note: The MSR address is derived from the perspective

of the CPU Core. See Section 4.1 "MSR Set" on

page 45 for more details on MSR addressing.

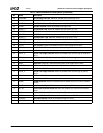

Table 6-85. Standard GeodeLink™ Device MSRs Summary

MSR

Address Type Register Name Reset Value Reference

4C002000h RO GLD Capabilities MSR (GLD_MSR_CAP) 00000000_00002400h Page 541

4C002001h R/W GLD Master Configuration MSR

(GLD_MSR_CONFIG)

00000000_00000000h Page 541

4C002002h R/W GLD SMI MSR (GLD_MSR_SMI) 00000000_0000001Fh Page 542

4C002003h R/W GLD Error MSR (GLD_MSR_ERROR) 00000000_00000000h Page 543

4C002004h R/W GLD Power Management MSR

(GLD_MSR_PM)

00000000_00000015h Page 544

4C002005h R/W GLD Diagnostic MSR (GLD_MSR_DIAG) 00000000_00000000h Page 544

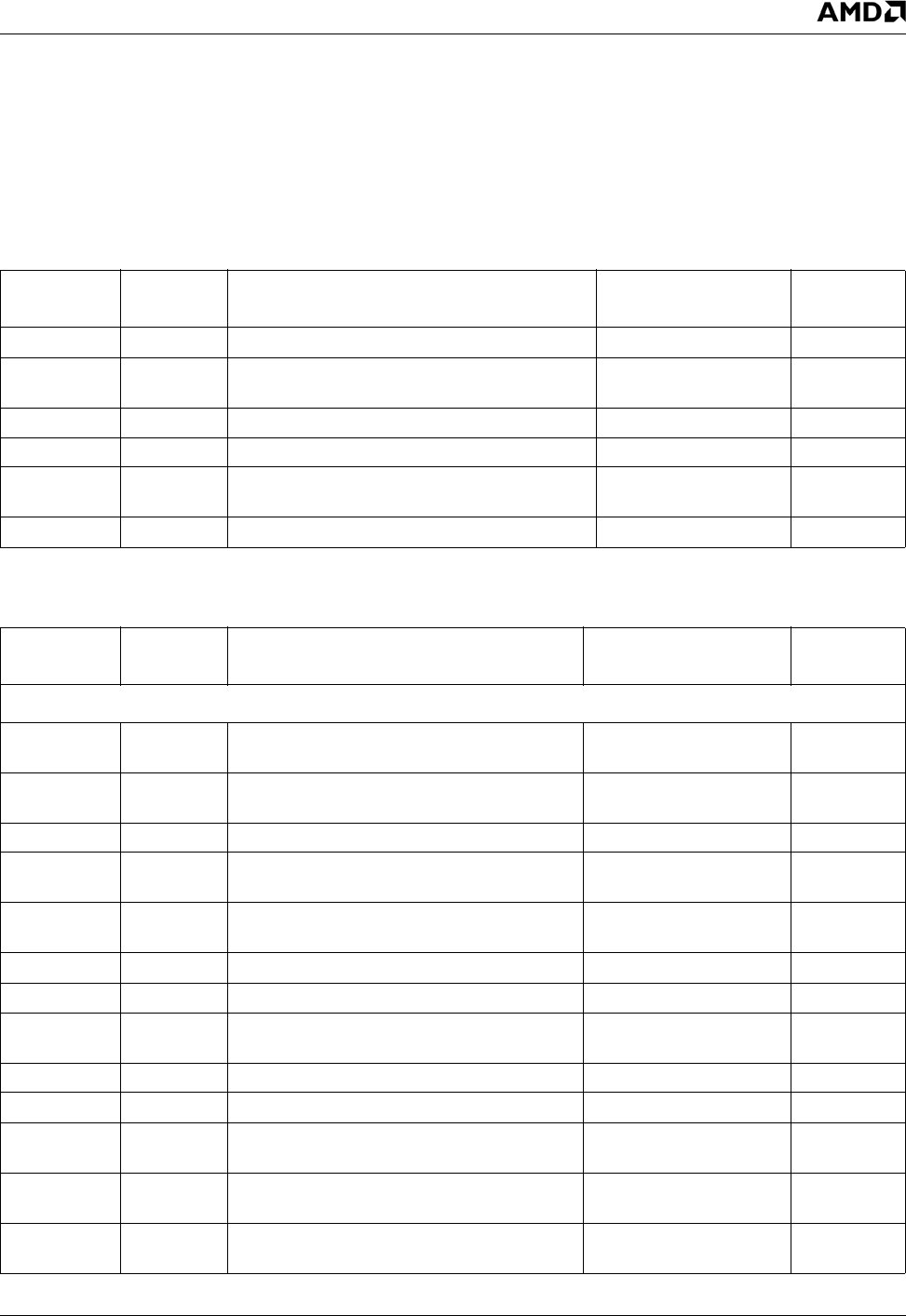

Table 6-86. GLCP Specific MSRs Summary

MSR

Address Type Register Name Reset Value Reference

GLCP Control MSRs

4C000008h R/W GLCP Clock Disable Delay Value

(GLCP_CLK_DIS_DELAY)

00000000_00000000h Page 545

4C000009h R/W GLCP Clock Mask for Sleep Request

(GLCP_PMCLKDISABLE)

00000000_00000000h Page 545

4C00000Ah RO Chip Fabrication Information (GLCP_FAB) 00000000_00000001h Page 547

4C00000Bh R/W GLCP Global Power Management Controls

(GLCP_GLB_PM)

00000000_00000000h Page 547

4C00000Ch R/W GLCP Debug Output from Chip

(GLCP_DBGOUT)

00000000 00000000h Page 548

4C00000Dh R/W GLCP Processor Status (GLCP_PROCSTAT) Bootstrap Dependant Page 548

4C00000Eh R/W GLCP DOWSER (GLCP_DOWSER) 00000000_00000000h Page 549

4C00000Fh R/W GLCP I/O Delay Controls

(GLCP_DELAY_CONTROLS)

00000000_00000000h Page 549

4C000010h R/W GLCP Clock Control (GLCP_CLKOFF) 00000000_00000000h Page 551

4C000011h RO GLCP Clock Active (GLCP_CLKACTIVE) Input Determined Page 552

4C000012h R/W GLCP Clock Mask for Debug Clock Stop

Action (GLCP_CLKDISABLE)

00000000_00000000h Page 553

4C000013h R/W GLCP Clock Active Mask for Suspend

Acknowledge (GLCP_CLK4ACK)

00000000_00000000h Page 553

4C000014h R/W GLCP System Reset and PLL Control

(GLCP_SYS_RSTPLL)

Bootstrap specific Page 554