38 AMD Geode™ LX Processors Data Book

Signal Definitions

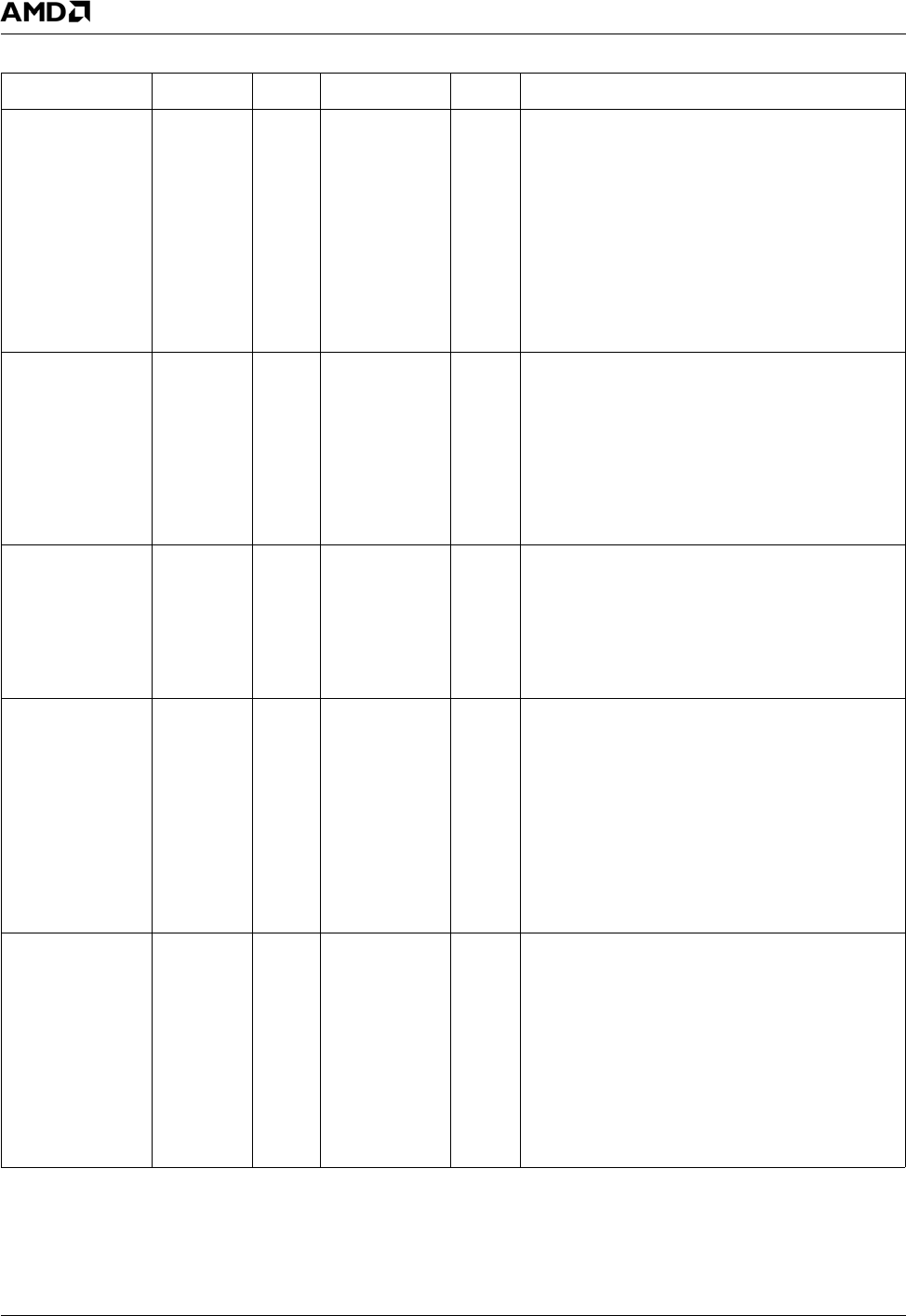

33234H

RESET# Y30 I 0-1 Mb/s 3.3 PCI Reset. RESET# aborts all operations in

progress and places the AMD Geode LX proces-

sor into a reset state. RESET# forces the CPU

and peripheral functions to begin executing at a

known state. All data in the on-chip cache is

invalidated upon a reset.

RESET# is an asynchronous input, but must

meet specified setup and hold times to guarantee

recognition at a particular clock edge. This input

is typically generated during the power-on-reset

(POR) sequence.

STOP# AJ25 I/O 33-66 Mb/s 3.3 Target Stop. STOP# is asserted to indicate that

the current target is requesting the master to stop

the current transaction. This signal is used with

DEVSEL# to indicate retry, disconnect, or target

abort. If STOP# is sampled active while a master,

FRAME# is de-asserted and the cycle is stopped

within three SYSREFs. STOP# can be asserted

when the PCI write buffers are full or a previously

buffered cycle has not completed.

FRAME# AL28 I/O 33-66 Mb/s 3.3 Frame. FRAME# is driven by the current master

to indicate the beginning and duration of an

access. FRAME# is asserted to indicate a bus

transaction is beginning. While FRAME# is

asserted, data transfers continue. When

FRAME# is de-asserted, the transaction is in the

final data phase.

IRDY# AH25 I/O 33-66 Mb/s 3.3 Initiator Ready. IRDY# is asserted to indicate

that the bus master is able to complete the cur-

rent data phase of the transaction. IRDY# is used

in conjunction with TRDY#. A data phase is com-

pleted on any SYSREF in which both IRDY# and

TRDY# are sampled asserted. During a write,

IRDY# indicates valid data is present on

AD[31:0]. During a read, it indicates the master is

prepared to accept data. Wait cycles are inserted

until both IRDY# and TRDY# are asserted

together.

TRDY# AK26 I/O 33-66 Mb/s 3.3 Target Ready. TRDY# is asserted to indicate that

the target agent is able to complete the current

data phase of the transaction. TRDY# is used in

conjunction with IRDY#. A data phase is com-

plete on any SYSREF in which both TRDY# and

IRDY# are sampled asserted. During a read,

TRDY# indicates that valid data is present on

AD[31:0]. During a write, it indicates the target is

prepared to accept data. Wait cycles are inserted

until both IRDY# and TRDY# are asserted

together.

3.4.5 PCI Interface Signals (Continued)

Signal Name Ball No. Type f V Description