562 AMD Geode™ LX Processors Data Book

GeodeLink™ Control Processor Register Descriptions

33234H

6.14.2.21 GLCP Processor Throttle Off Delay (GLCP_TH_OD)

6.14.3 GLCP IGNNE I/Os

The GLCP’s GLIU is responsible for all the GLIU functionality. The GLCP’s GLIU implements a large MSR space consisting

of the required standard GLIU device MSRs, MSR controls for clock and PLL interfacing, the MSR controls for the I/O com-

panion modes and MVPI signals, and MSR controls for the debug logic. The GLCP’s GLIU must properly decode all possi-

ble GLIU transaction types including the unexpected addresses, request types and sizes. It must respond with the proper

number of response packets. In addition, it provides error logic to detect unexpected addresses and types.

The GLCP’s GLIU also implements the processor floating point exception handling logic.

always @(va_ferr or irq13 or write_to_F0F1 or ignee)

if (!va_ferr) nxt_ignne = 0;

else if (irq13 && write_to_F0F1) nxt_ignne = 1;

else nxt_ignne = ignne;

always @(posege ck)

ignee <= nxt_ignne;

irq13 <= va_ferr & !nxt_ignne;

The GLCP’s GLIU maintains MSRs that control the source and value of the companion device system outputs. It also con-

trols the current companion device mode.

Read data returns GLD_MSR_CAP data.

MSR Address 4C00001Eh

Type R/W - I/O Offset 18h

Reset Value 00000000_00000000h

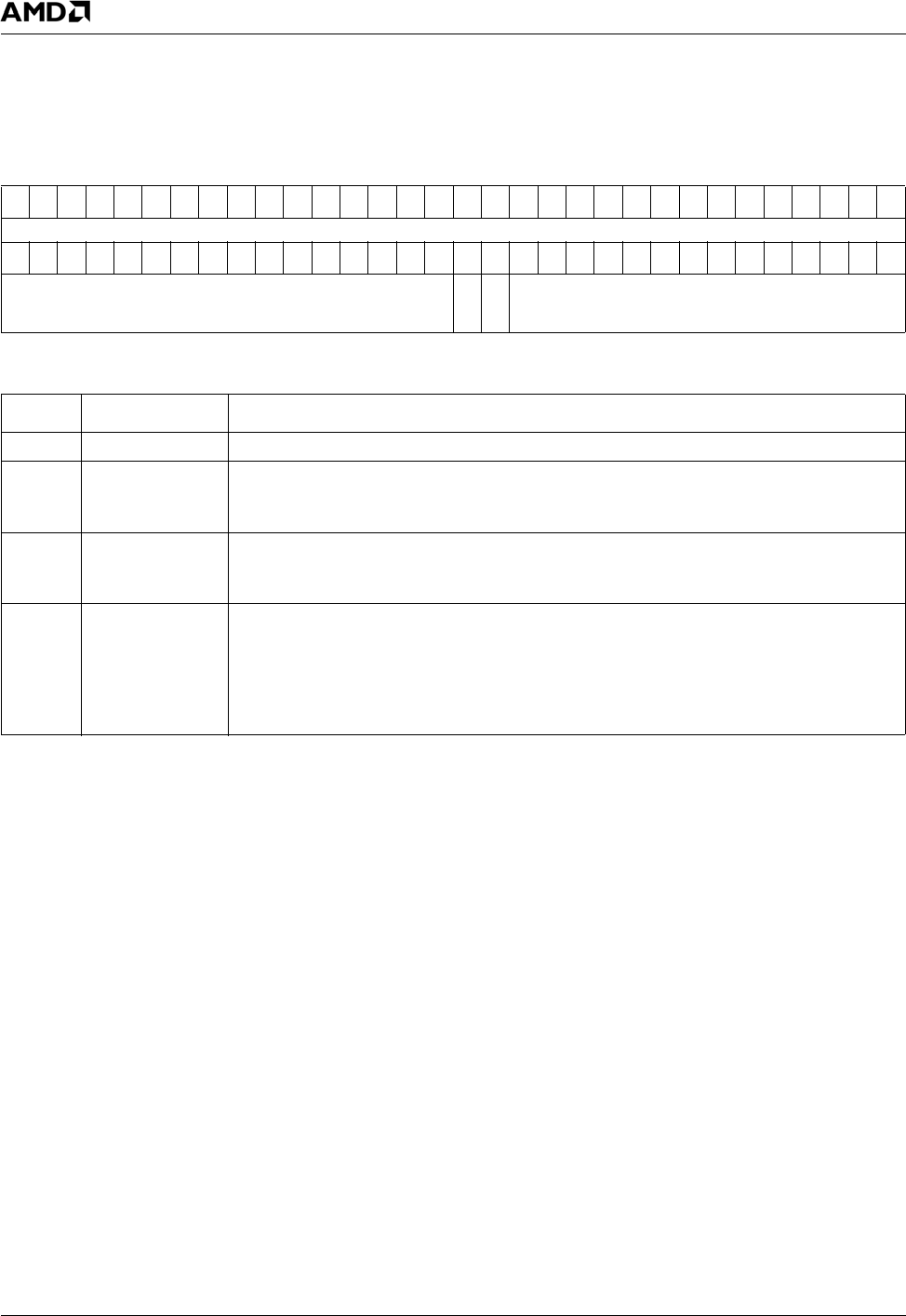

GLCP_TH_OD Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

IRQ_EN

SMI_EN

OFF_DELAY

GLCP_TH_OD Bit Descriptions

Bit Name Description

63:16 RSVD Reserved. By convention, always write 0.

15 IRQ_EN Enable Throttling Restart after IRQ. If this bit is set and throttling is not disabled during

the IRQ handling, throttling restarts after the period specified by OFF_DELAY (bits

[13:0]). If this bit is clear, then an IRQ clears THT_EN (MSR 4C000018h[4]).

14 SMI_EN Enable Throttling Restart after SMI. If this bit is set and throttling is not disabled during

the SMI handling, throttling restarts after the period specified by OFF_DELAY (bits

[13:0])If this bit is clear, then an ASMI clears THT_EN (MSR 4C000018h[4]).

13:0 OFF_DELAY Throttle Off Delay. Indicates the period to wait from receipt of IRQ_EN (bit 15) or

SMI_EN (bit 14) before restarting throttle operation. This setting is multiplied by 16 to get

the number of PCI clock cycles to wait. If the OFF_DELAY has not expired and another

IRQ or SMI occurs, the OFF_DELAY timer is cleared again and the wait begins again.

Setting OFF_DELAY to 0 results in only one PCI clock cycle of throttling being disabled

after an IRQ or SMI.

GLCP I/O Offset F0h, F1h

Typ e W

Reset Value NA