AMD Geode™ LX Processors Data Book 191

CPU Core Register Descriptions

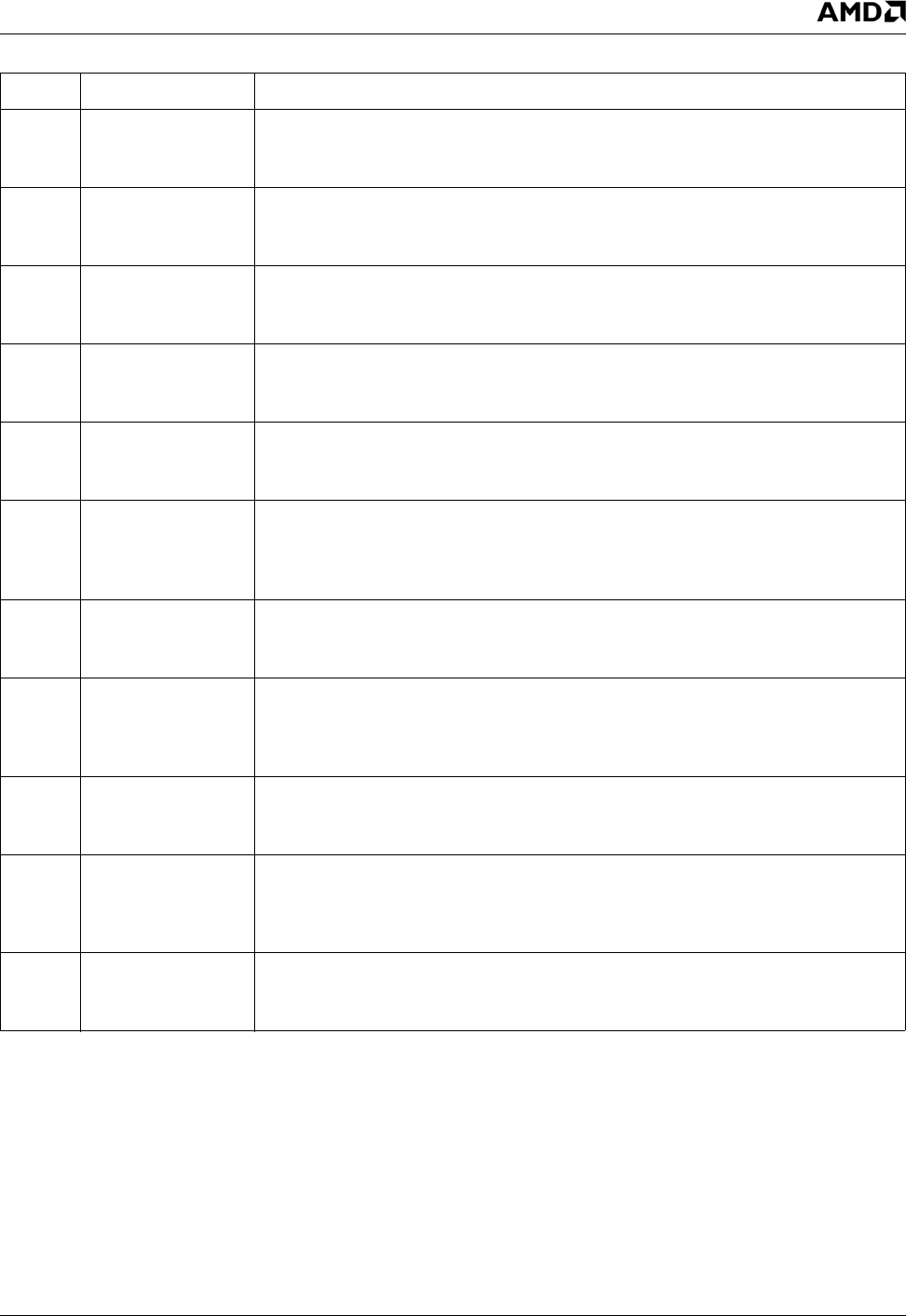

33234H

10 BIST_TAG_GO_

WAY3 (RO)

L2 Cache Tag BIST Way 3 Result (Read Only).

0: Fail. (Default)

1: Pass.

9 BIST_TAG_GO_

WAY2 (RO)

L2 Cache Tag BIST Way 2 Result (Read Only).

0: Fail. (Default)

1: Pass.

8 BIST_TAG_GO_

WAY1 (RO)

L2 Cache Tag BIST Way 1 Result (Read Only).

0: Fail. (Default)

1: Pass.

7 BIST_TAG_GO_

WAY0 (RO)

L2 Cache Tag BIST Way 0 Result (Read Only).

0: Fail. (Default)

1: Pass.

6 BIST_TAG_GO

(RO)

L2 Cache Tag BIST Result (Read Only).

0: Fail. (Default)

1: Pass.

5 BIST_MRU_DRT_

EN

L2 Cache Most Recently Used Data Retention Timer BIST Enable. Enable the

data retention timer for the MRU BIST.

0: Disable. (Default)

1: Enable

4BIST_MRU_EN L2 Cache Most Recently Used BIST Enable. Start MRU BIST (on a write).

0: Disable. (Default)

1: Enable

3BIST_DATA_

DRT_EN

L2 Cache Data Retention Timer BIST Enable. Enable data retention timer for the

data BIST.

0: Disable. (Default)

1: Enable

2BIST_DATA_EN L2 Cache Data BIST Enable. Start data BIST (on a write).

0: Don’t start BIST. (Default)

1: Start BIST

1BIST_TAG_

DRT_EN

L2 Cache Tag Data Retention Timer BIST Enable. Enable Data Retention timer for

the Tag BIST.

0: Disable. (Default)

1: Enable

0BIST_TAG_EN L2 Cache Tag BIST Enable. Start Tag BIST (on a write).

0: Don’t start BIST. (Default)

1: Start BIST

L2_BIST_MSR Bit Descriptions (Continued)

Bit Name Description