48 AMD Geode™ LX Processors Data Book

GeodeLink™ Interface Unit

33234H

Each memory request is compared against all the P2D

descriptors. If the memory request does not hit in any of

the descriptors, the request is sent to the subtractive port. If

the memory requests hit more than one descriptor, the

results are undefined. The software must provide a consis-

tent non-overlapping address map.

The way each descriptor checks if the request address hits

its descriptor and how to route the request address to the

device address is described in Table 4-3.

P2D Base Mask Descriptor (P2D_BM)

P2D_BM is the simplest descriptor. It usually maps a power

of two size aligned region of memory to a destination ID.

P2D_BM performs no address translation.

P2D Base Mask Offset Descriptor (P2D_BMO)

P2D_BMO has the same routing features as P2D_BM with

the addition of a 2s complement address translation to the

most-significant bits of the address.

P2D Range Descriptor (P2D_R)

P2D_R maps a range of addresses to a device that is NOT

a power of 2 size aligned. There is no address translation

(see Table 4-3).

P2D Range Offset Descriptor (P2D_RO)

P2D_RO has the same address routing as P2D_R with the

addition of address translation with a 2s complement off-

set.

P2D Swiss Cheese Descriptor (P2D_SC)

The P2D_SC maps a 256 KB region of memory in 16 KB

chunks to a device or the subtractive decode port. The

descriptor type is useful for legacy address mapping. The

Swiss cheese feature implies that the descriptor is used to

“poke holes” in memory.

Note: Only one P2D can hit at a time for a given port. If

the P2D descriptors are overlapping, the results

are undefined.

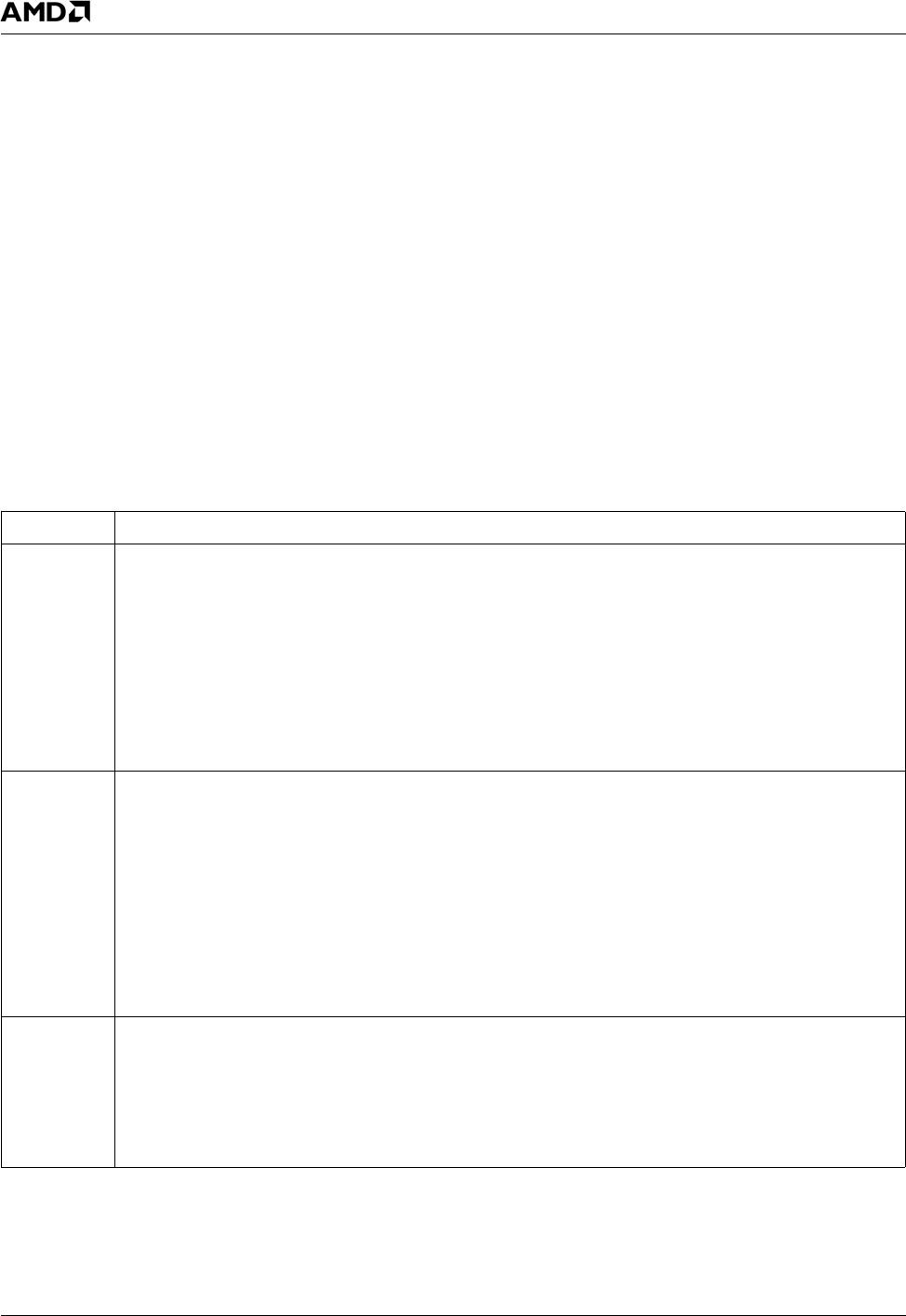

Table 4-3. GLIU Memory Descriptor Address Hit and Routing Description

Descriptor Function Description

P2D_BM,

P2D_BMO

Checks that the physical address supplied by the device’s request on address bits [31:12] with a logical AND with

PMASK bits of the descriptor register bits [19:0] are equal to the PBASE bits on the descriptor register (bits [39:20]).

Also checks that the BIZZARO bit of the request is equal to the PCMP_BIZ bit of the descriptor register bit [60].

If the above matches, then the descriptor has a hit condition and it routes the received address to the programmed des-

tination PDID1 of the descriptor register (bits [63:61]).

For P2D_BM:

DEVICE_ADDR = request address

For P2D_BMO:

DEVICE_ADDR [31:12] = [request address [31:12] + descriptor POFFSET]

DEVICE_ADDR [11:0] = request address [11:0]

P2D_R,

P2D_RO

Checks that the physical address supplied by the device’s request on address bits [31:12] are within the range speci-

fied by PMIN and PMASK field bits [39:20] and [19:0], respective of the descriptor register. PMIN is the minimum

address range and PMAX is the maximum address range.The condition is: PMAX > physical address [31:12] > PMIN.

Also checks that the BIZZARO bit of the request is equal to the PCMP_BIZ bit of the descriptor register bit [60].

If the above matches, then the descriptor has a hit condition and routes the received address to the programmed des-

tination ID, PDID1 of the descriptor register (bits [63:61]).

For P2D_R:

DEVICE_ADDR = request address

For P2D_RO:

DEVICE_ADDR [31:12] = [request address [31:12] + descriptor POFFSET]

DEVICE_ADDR [11:0] = request address [11:0]

P2D_SC Checks that the physical address supplied by the device’s request on address bits [31:18] are equal to the PBASE field

of descriptor register bits [13:0] and that the enable write or read conditions given by the descriptor register fields WEN

and REN in bits [47:32] and [31:16], respectively matches the request type and enable fields given on the physical

address bits [17:14] of the device’s request.

If the above matches, then the descriptor has a hit condition and routes the received address to the programmed des-

tination ID, PDID1 field of the descriptor register bits [63:61].

DEVICE_ADDR = request address