338 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

6.6.8 Video Downscaling

6.6.8.1 DC Video Downscaling Delta (DC_VID_DS_DELTA)

This register is provided to allow downscaling of the video overlay image by selective skipping of source lines. A DDA

engine is used to identify lines to be skipped according to the following algorithm:

At vertical retrace:

PHASE = 0; // clear PHASE initially

skip_flag = 0; // never skip the first line

linenum = 0; // point to first line

For each line of video: send_video_line(linenum); // send line to DF

linenum++ // increment to next line

{skip_flag, PHASE} = PHASE + DELTA; // skip_flag is carry from add

if (skip_flag) linenum = linenum + 1 // skip an additional line if flag was set

else linenum = linenum // otherwise, just skip n lines

The value to program into DC_VID_DS_DELTA is calculated as follows:

parms: DWORD ORIGINAL_LINES = full size image line count

DWORD SCALED_LINES = line count of scaled image equation:

DWORD DC_VID_DS_DELTA = ((ORIGINAL_LINES << 14) / SCALED_LINES) << 18;

Note: The scaling algorithm is only intended to work for ratios from 1 down to 1/2. The equation above clips the value to

the 14 bits of accuracy in the hardware. The equation could be modified to allow for higher bits in the future by

changing the 14-bit and 18-bit shift values. The only requirement is that the sum of the shift values be 32.

DC Memory Offset 080h

Typ e R /W

Reset Value 00000000h

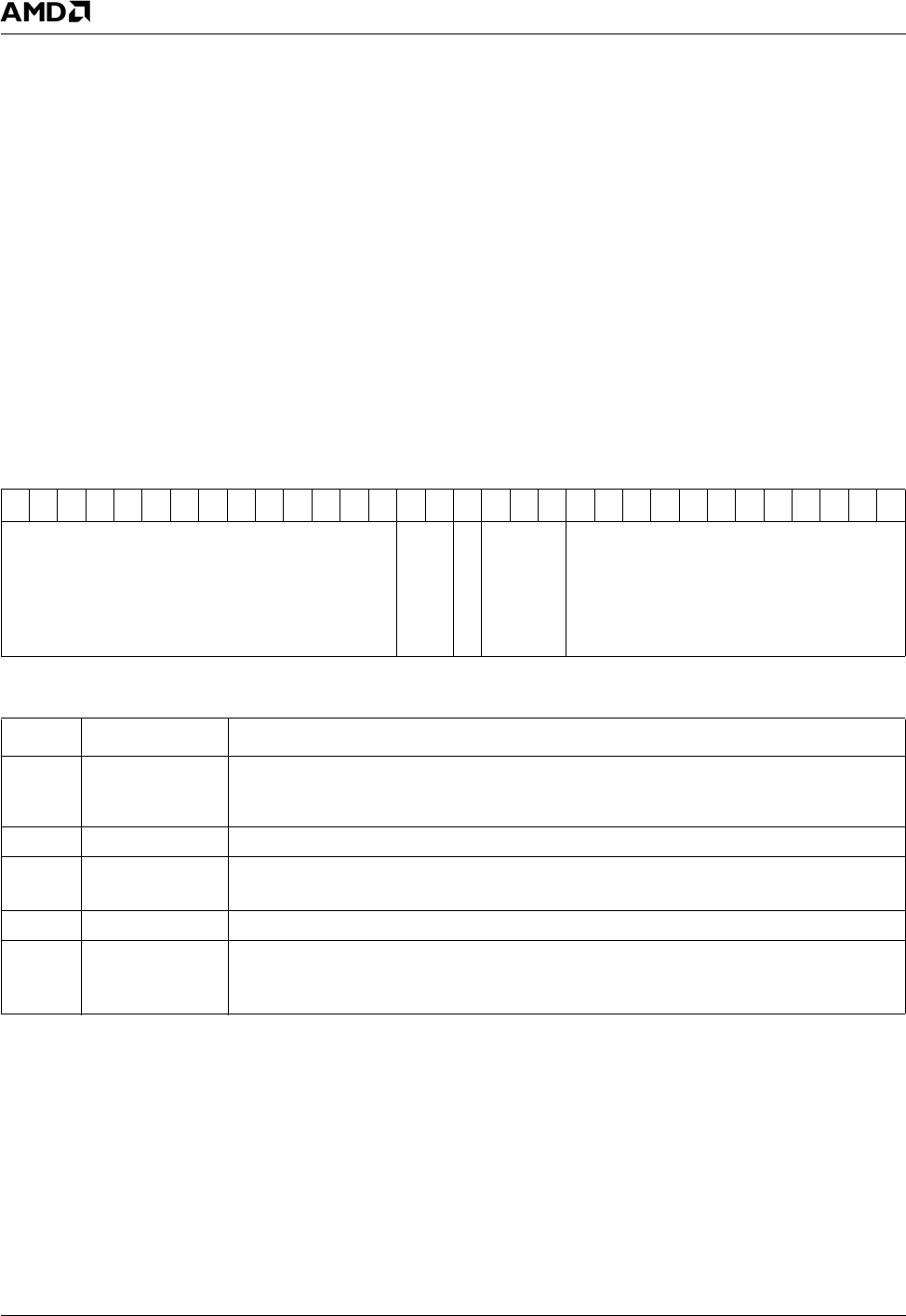

DC_VID_DS_DELTA Register Map

313029282726252423222120191817161514131211109876543210

DELTA RSVD

VSYNC_SHIFT_EN

RSVD VSYNC_SHIFT

DC_VID_DS_DELTA Bit Descriptions

Bit Name Description

31:18 DELTA Delta. A 0.14 fixed-point fraction used as the delta value for the DDA engine that calcu-

lates which video lines to skip for video downscaling. This register is enabled when the

VDSE bit in DC_GENERAL_CFG is set (DC Memory Offset 004h[19] = 1).

17:16 RSVD Reserved.

15 VSYNC_SHIFT_

EN

VSYNC Shift Enable. When this bit is set, the VSYNC output is delayed during even

fields in interlaced modes. The amount of delay is defined in VSYNC_SHIFT (bits [11:0]).

14:12 RSVD Reserved.

11:0 VSYNC_SHIFT

VSYNC Shift. When VSYNC_SHIFT_EN is set (bit 15 = 1), this field determines the

number of dot clocks of delay that is inserted on VSYNC during even fields in interlaced

modes.