60 AMD Geode™ LX Processors Data Book

GLIU Register Descriptions

33234H

4.2.1.6 GLD Diagnostic MSR (GLD_MSR_DIAG)

This register is reserved for internal use by AMD and should not be written to.

4.2.2 GLIU Specific Registers

4.2.2.1 Coherency (COH)

GLD

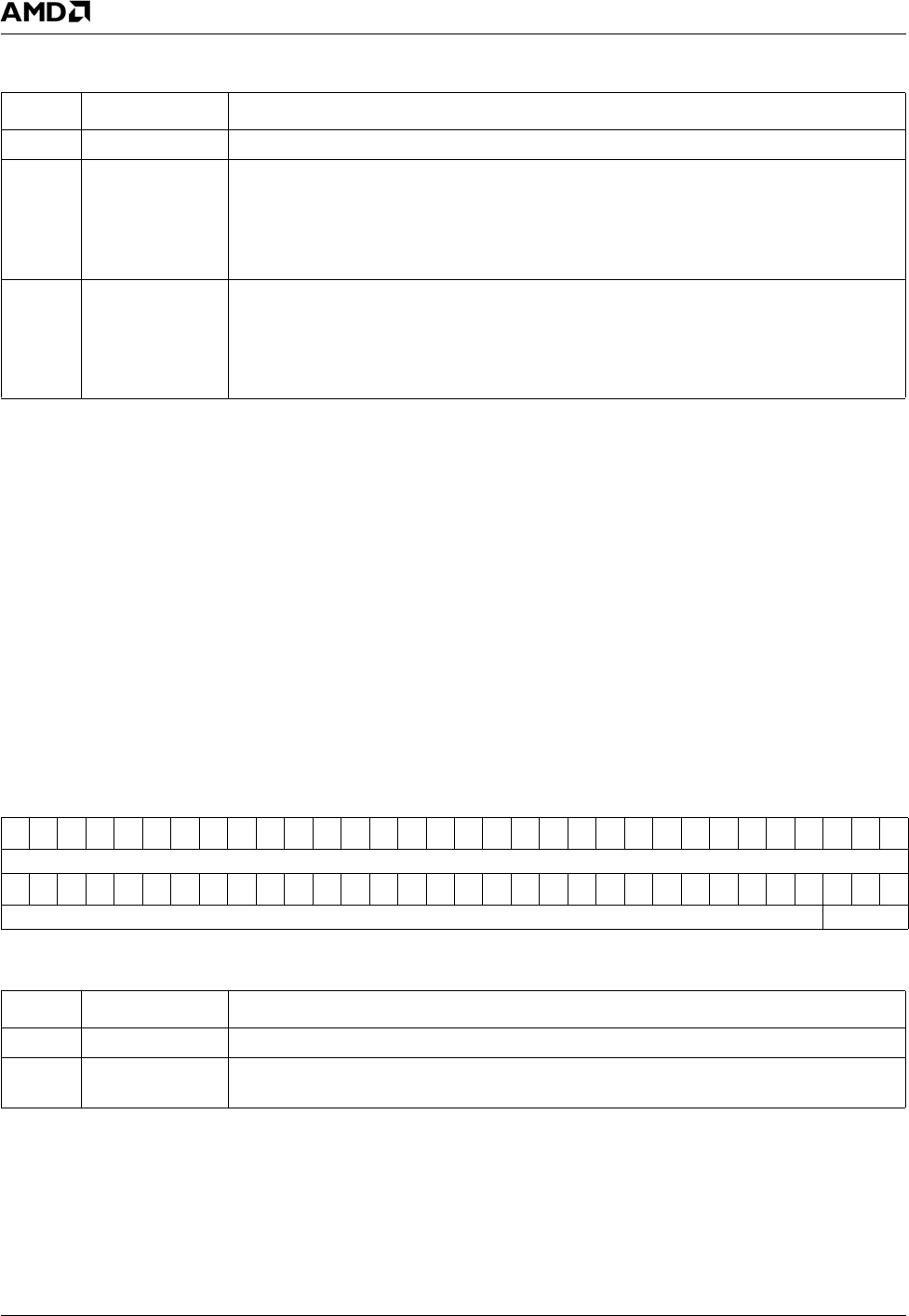

_MSR_PM Bit Descriptions

Bit Name Description

63:4 RSVD Reserved.

3:2 PMODE_1 Power Mode 1. Statistics and Time Slice Counters.

00: Disable clock gating. Clocks are always on.

01: Enable hardware clock gating. Clock goes off whenever this module’s circuits are not

busy.

10, 11: Reserved.

1:0 PMODE_0 Power Mode 0. Online GLIU logic.

00: Disable clock gating. Clocks are always on.

01: Enable hardware clock gating. Clock goes off whenever this module’s circuits are not

busy.

10, 11: Reserved.

MSR Address GLIU0: 10002005h

GLIU1: 40002005h

Typ e R /W

Reset Value 00000000_00000000h

MSR Address GLIU0: 10000080h

GLIU1: 40000080h

Typ e R /W

Reset Value Configuration Dependent

COH Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD COHP

COH Bit Descriptions

Bit Name Description

63:3 RSVD Reserved.

2:0 COHP Coherent Device Port. The port that coherents snoops are routed to. If the coherent

device is on the other side of a bridge, the COHP points to the bridge.