250 AMD Geode™ LX Processors Data Book

Graphics Processor

33234H

6.3.8.2 Host Source

For source data that is not already in the frame buffer

region of memory, software can use the GP_HST_SRC

register (GP Memory Offset 48h) for loading the data into

the Graphics Processor. This is achieved by selecting host

source as the origination of the source data when setting

up the BLT. After writing to the GP_BLT_MODE register

(GP Memory Offset 40h) to initiate the BLT, software must

first check to make sure that the host source BLT is active

by checking that the BP bit of the GP_BLT_STATUS regis-

ter (GP Memory Offset 44h[0]) is not set before proceeding

with successive writes to the GP_HST_SRC register (GP

Memory Offset 48h). Enough writes must be generated to

complete the requested BLT operation. Any extra writes, or

writes when host source data is not required, are ignored,

not saved, and will not be used for the next BLT. Writes to

this register are buffered into the source FIFO to decouple

the processor from the Graphics Processor. The source

FIFO is currently two cache lines deep, allowing the pro-

cessor to load up to 64 bytes of data. If more data is

needed, the driver can then poll the SHE (Source FIFO

Half Empty) bit of the GP_BLT_STATUS register (GP

Memory Offset 44h[3]). When this bit is set, the source

FIFO can accept at least one more cache line of data. Writ-

ing to the Graphics Processor while the Host Source FIFO

is full causes the Graphics Processor to drop the writes,

which means that the BLT is corrupt and most likely will not

complete. Since there is not enough host source data left,

the Graphics Processor hangs waiting for more source

data.

The two LSBs of the source OFFSET are used to deter-

mine the starting byte of the host source data and the

XLSBs are used in the case of monochrome source data to

determine the starting bit. The starting pixel of the source

data is aligned to the starting pixel of the destination data

by the hardware. In monochrome byte-packed mode, the

hardware begins BLTing at the specified pixel, and after

WIDTH pixels have been transferred, skips the remaining

bits in the byte plus the number specified in XLSBs, and

begins the next line at that location. In unpacked mono-

chrome mode or color mode, the hardware discards any

data remaining in the DWORD after WIDTH pixels have

been transferred and begins the next line at the byte speci-

fied by the two LSBs of the offset in the next DWORD

received. Examples of these two modes are shown in Table

6-23 and Table 6-24, with OFFSET set to 0h, XLSBs set to

2h, and WIDTH set to 8h.

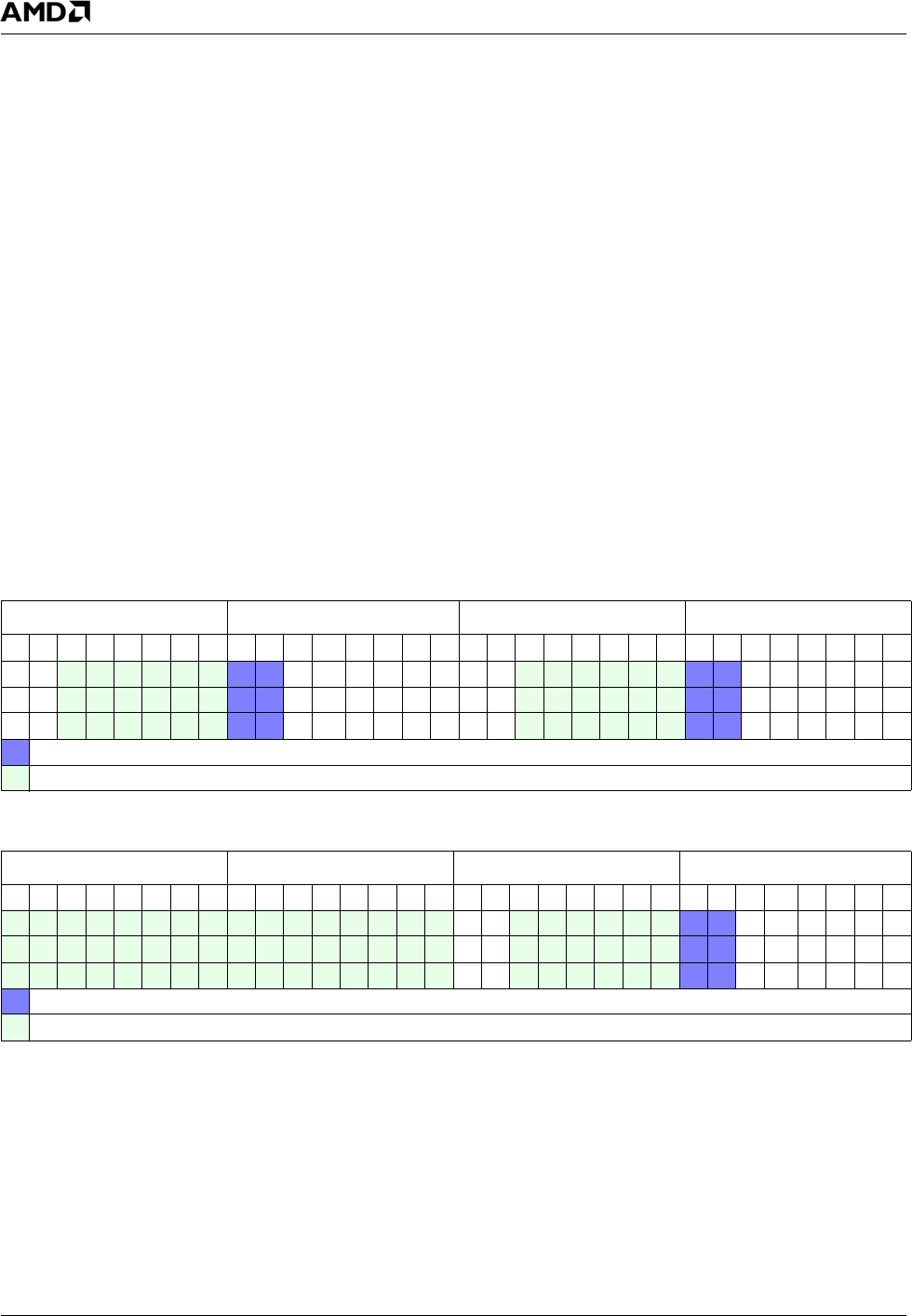

Table 6-23. Example of Byte-Packed Monochrome Source Data

Byte 3 Byte 2 Byte 1 Byte 0

01234567012 3 45670123456701234567

16 17

101 1121314150607 00 01 02 03 04 05

36 37 30 31 32 33 34 35 26 27 20 21 22 23 24 25

56 57

50 51 52 53 54 55 46 47 40 41 42 43 44 45

Skip specified by XLSBs

Trailing bits at end of line

Table 6-24. Example of Unpacked Monochrome Source Data

Byte 3 Byte 2 Byte 1 Byte 0

012345670123456701234567012 3 4567

06 07 00 01 02 03 04 05

16 17 101 112131415

26 27 20 21 22 23 24 25

Skip specified by XLSBs

Trailing bits at end of line