520 AMD Geode™ LX Processors Data Book

Security Block Register Descriptions

33234H

6.12.3 Security Block Configuration/Control Registers

6.12.3.1 SB Control A (SB_CTL_A)

2 SBI Swap Bits. This bit controls a bit-swapping feature within the AES module. When set,

the bits within each byte are swapped on both AES DMA reads and writes. Bit 7 is

swapped with bit 0, bit 6 is swapped with 1, etc. Asserting this bit does not affect the

slave operations to AES registers, (including the writable key), nor does it affect

EEPROM operations. When this bit is cleared, the DMA operations read and write bytes

with the same bit order as they appear in memory.

1:0 DIV AES Enable Divider. These two bits control the ratio between the GLIU clock frequency

and the updating of the AES encryption engine registers. The AES module is clocked at

the GLIU frequency, however, the state registers only update on an enable pulse that

occurs each n cycles, where n is determined by the DIV value. This register should not

be changed during an AES operation.

00: Divide by 1 (use for 100 MHz GLIU or less).

01: Divide by 2 (use for 100 MHz to 200 MHz GLIU).

10: Divide by 3 (use for 200 MHz to 300 MHz GLIU).

11: Divide by 4 (use for 300 MHz to 400 MHz GLIU).

SB Memory Offset 000h

Typ e R /W

Reset Value 00000000h

GLD_MSR_CTRL Bit Descriptions (Continued)

Bit Name Description

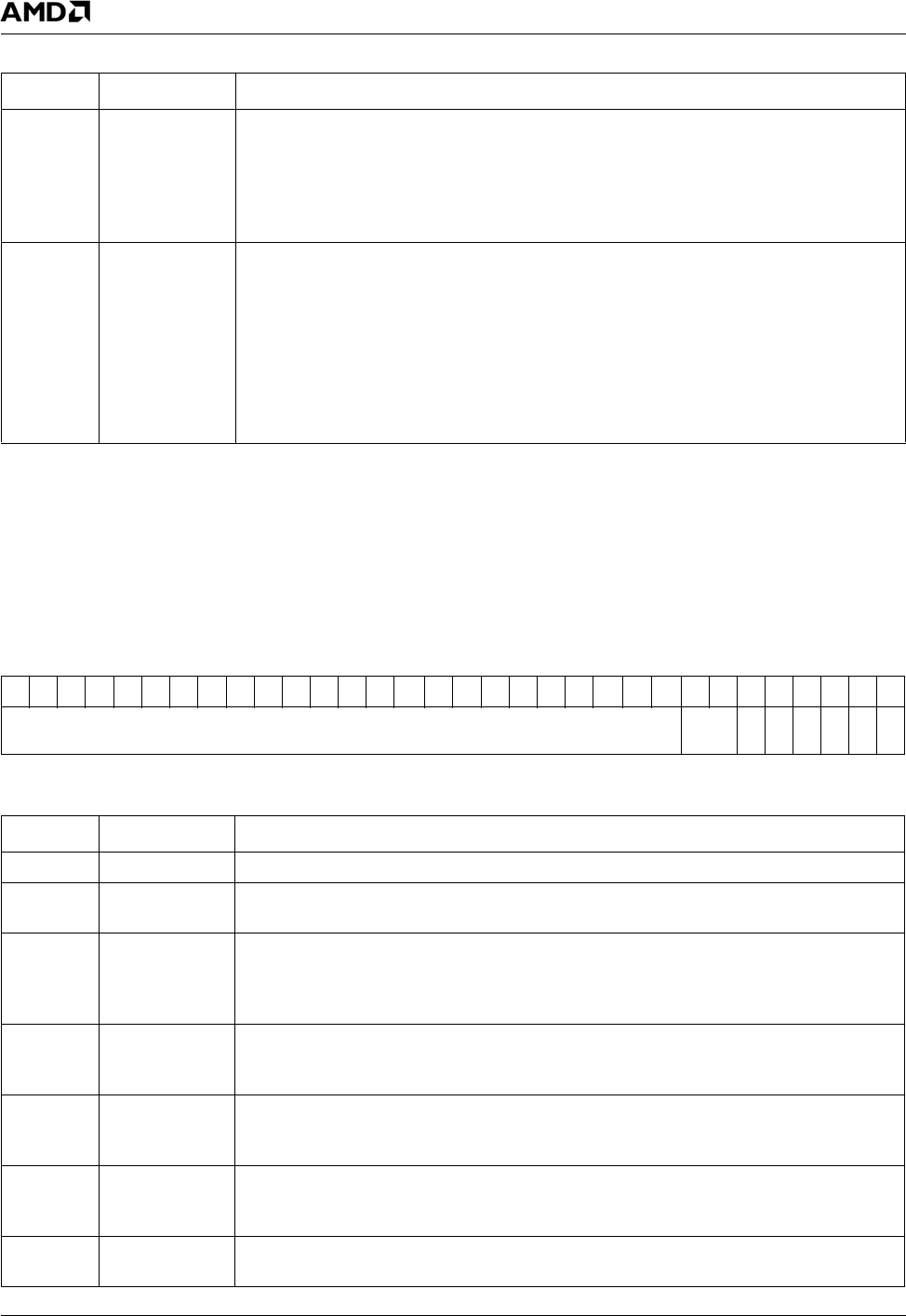

SB_CTL_A Register Map

313029282726252423222120191817161514131211109876543210

RSVD RSVD

CBCA

SCA

DCA

WKA

ECA

STA

SB_CTL_A Register Bit Descriptions

Bit Name Description

31:8 RSVD Reserved.

7:6 RSVD Reserved. These bits are implemented but reserved for future use. When writing to this

register, software should set these bits to 0 and ignore them on read.

5CBCA Cipher Block Chaining (CBC) Mode for A Pointer. When set, the AES engine

encrypts/decrypts using the Cipher Block Chaining Mode for the A pointer. When reset,

the AES engine encrypts/decrypts using the Electronic Codebook (ECB) Mode. No ini-

tialization vector is used when in ECB mode.

4SCA Source Coherency for A Pointer Set. When set, the source memory fetches using the

GLIU interface are flagged as coherent operations. When reset, the operations are non-

coherent.

3 DCA Destination Coherency for A Pointer Set. When set, the destination memory writes

using the GLIU interface are flagged as coherent operations. When reset, the opera-

tions are non-coherent.

2WKA Writable Key for A Pointer Set. When set, the AES engine uses the key from the writ-

able key register (SB Memory Offset 030h-03Ch) for its next operation. When reset, it

uses the hidden key value.

1ECA Encrypt for A Pointer. When set, the AES operates in encryption mode. When reset, it

operates in decryption mode.