AMD Geode™ LX Processors Data Book 585

GeodeLink™ PCI Bridge Register Descriptions

33234H

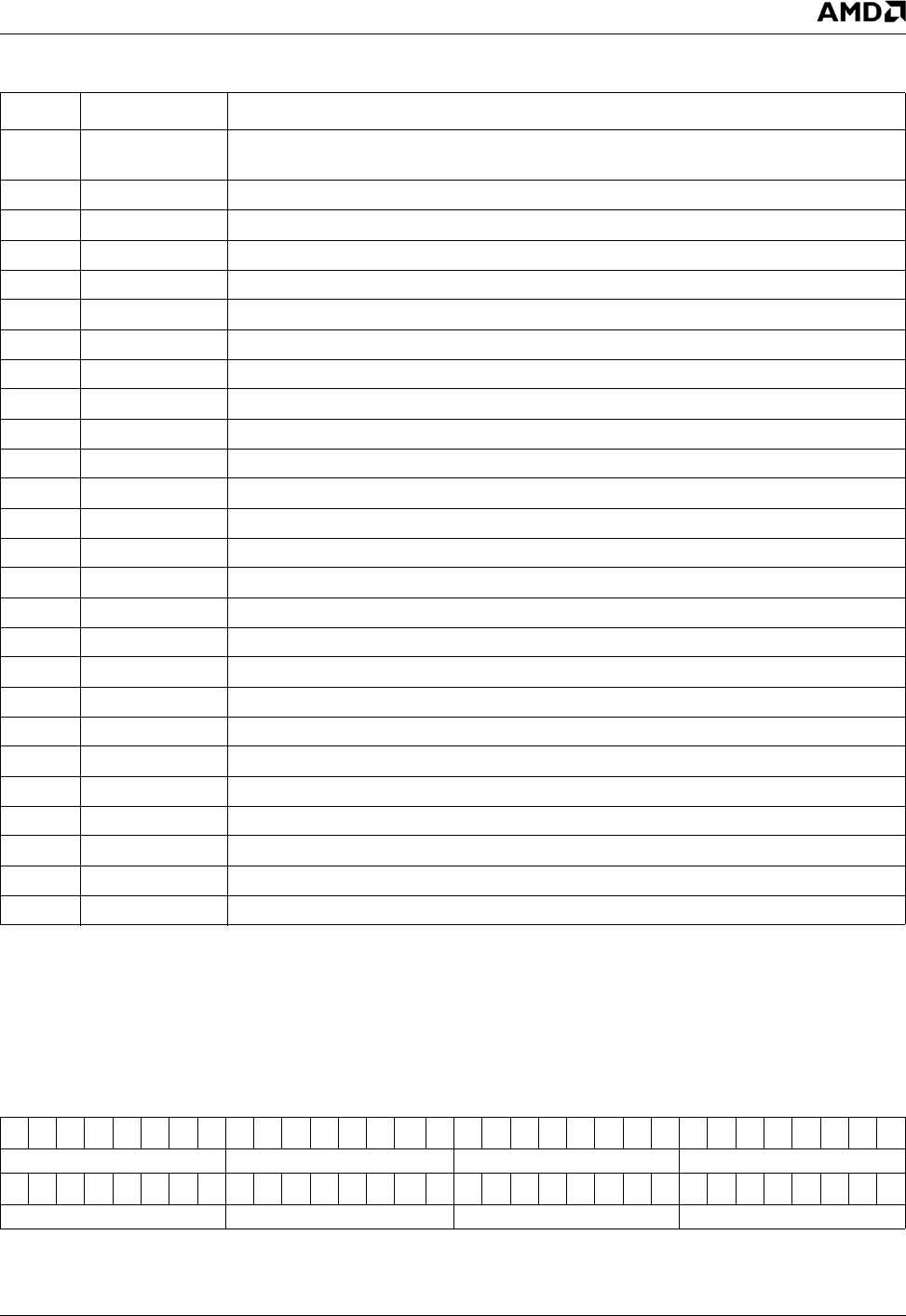

6.16.2.6 GLPCI Fixed Region Configuration A0-BF (GLPCI_A0)

GLPCI_REN Bit Descriptions

Bit Name Description

63:32 Spare Spare Bits. Extra bits available for future use. These bits may be set and cleared, but do

not control anything.

31:24 RSVD (RO) Reserved (Read Only). Reserved for future use

23 FC FC Enable. Enables memory access to FC000 through FFFFF from PCI.

22 F8 F8 Enable. Enables memory access to F8000 through FBFFF from PCI.

21 F4 F4 Enable. Enables memory access to F4000 through F7FFF from PCI.

20 F0 F0 Enable. Enables memory access to F0000 through F3FFF from PCI.

19 EC EC Enable. Enables memory access to EC000 through EFFFF from PCI.

18 E8 E8 Enable. Enables memory access to E8000 through EBFFF from PCI.

17 E4 E4 Enable. Enables memory access to E4000 through E7FFF from PCI.

16 E0 E0 Enable. Enables memory access to E0000 through E3FFF from PCI.

15 DC DC Enable. Enables memory access to DC000 through DFFFF from PCI.

14 D8 D8 Enable. Enables memory access to D8000 through DBFFF from PCI.

13 D4 D4 Enable. Enables memory access to D4000 through D7FFF from PCI.

12 D0 D0 Enable. Enables memory access to D0000 through D3FFF from PCI.

11 CC CC Enable. Enables memory access to CC000 through CFFFF from PCI.

10 C8 C8 Enable. Enables memory access to C8000 through CBFFF from PCI.

9C4 C4 Enable. Enables memory access to C4000 through C7FFF from PCI.

8C0 C0 Enable. Enables memory access to C0000 through C3FFF from PCI.

7BC BC Enable. Enables memory access to BC000 through BFFFF from PCI.

6B8 B8 Enable. Enables memory access to B8000 through BBFFF from PCI.

5B4 B4 Enable. Enables memory access to B4000 through B7FFF from PCI.

4B0 B0 Enable. Enables memory access to B0000 through B3FFF from PCI.

3AC AC Enable. Enables memory access to AC000 through AFFFF from PCI.

2A8 A8 Enable. Enables memory access to A8000 through ABFFF from PCI.

1A4 A4 Enable. Enables memory access to A4000 through A7FFF from PCI.

0A0 A0 Enable. Enables memory access to A0000 through A3FFF from PCI.

MSR Address 50002015h

Typ e R /W

Reset Value 00000000_00000000h

GLPCI_A0 Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

BC B8 B4 B0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AC A8 A4 A0