348 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

6.6.12.2 DC Color Key Mask (DC_CLR_KEY_MASK)

6.6.12.3 DC Color Key Horizontal Position (DC_CLR_KEY_X)

Settings written to this register do not take effect until the start of the following frame or interlaced field.

6.6.12.4 DC Color Key Vertical Position (DC_CLR_KEY_Y)

Settings written to this register do not take effect until the start of the following frame or interlaced field.

DC Memory Offset 0BCh

Typ e R /W

Reset Value 00xxxxxxh

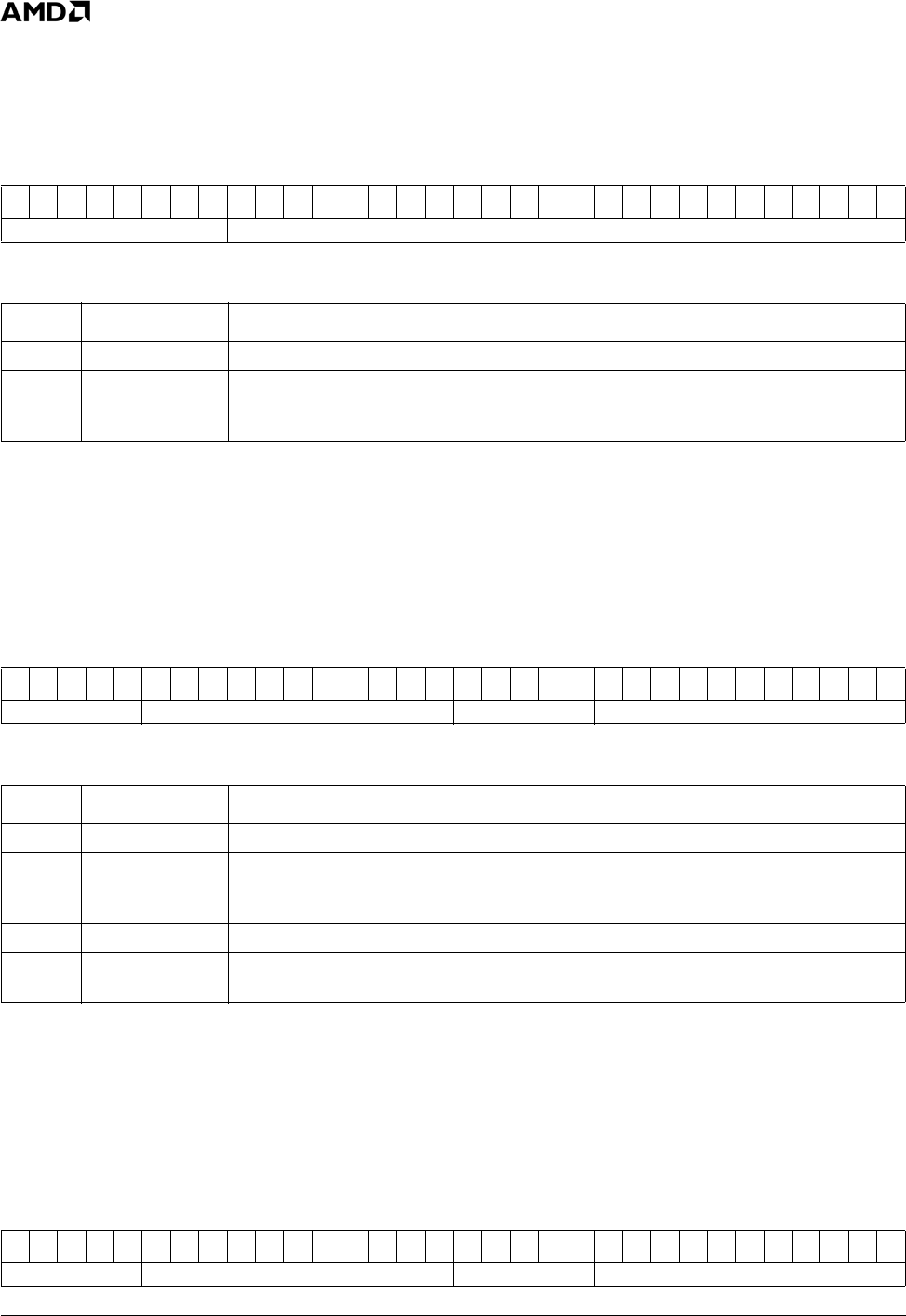

DC_CLR_KEY_MASK Register Map

313029282726252423222120191817161514131211109876543210

RSVD CLR_KEY_MASK

DC_CLR_KEY_MASK Bit Descriptions

Bit Name Description

31:24 RSVD Reserved. Set to 0.

23:0 CLR_KEY_

MASK

Color Key Mask. This field is ANDed with both the pixel and the color key value (in

DC_CLR_KEY, DC Memory Offset 0B8h[23:0]) before comparing the values. This allows

the value of some bits to be ignored when performing the match.

DC Memory Offset 0C0h

Typ e R /W

Reset Value 00000000h

DC_CLR_KEY_X Register Map

313029282726252423222120191817161514131211109876543210

RSVD CLR_KEY_X_END RSVD CLR_KEY_X_START

DC_CLR_KEY_X Bit Descriptions

Bit Name Description

31:27 RSVD Reserved. Set to 0.

26:16 CLR_KEY_X_

END

Color Key Horizontal End. This field indicates the horizontal end position of the color

key region minus 1.This represents the first pixel past the end of the color key region.

This field is 0-based; the upper left pixel of the screen is represented by (0,0).

15:11 RSVD Reserved. Set to 0.

10:0 CLR_KEY_X_

START

Color Key Horizontal Start. This field represents the horizontal start position of the color

key region minus 1. This represents the first pixel within the color key region.

DC Memory Offset 0C4h

Typ e R /W

Reset Value 00000000h

DC_CLR_KEY_Y Register Map

313029282726252423222120191817161514131211109876543210

RSVD CLR_KEY_Y_END RSVD CLR_KEY_Y_START