AMD Geode™ LX Processors Data Book 563

GeodeLink™ Control Processor Register Descriptions

33234H

6.14.4 GLCP Specific MSRs - GLCP Debug Interface MSRs

6.14.4.1 GLCP DAC (GLCP_DAC)

This register has DAC diagnostic controls and status. It ties directly to inputs and outputs on the DAC module.

Bits [13:11] of this register are only valid after the DAC is enabled.

MSR Address 4C000023h

Typ e R /W

Reset Value 00000000_00000000h

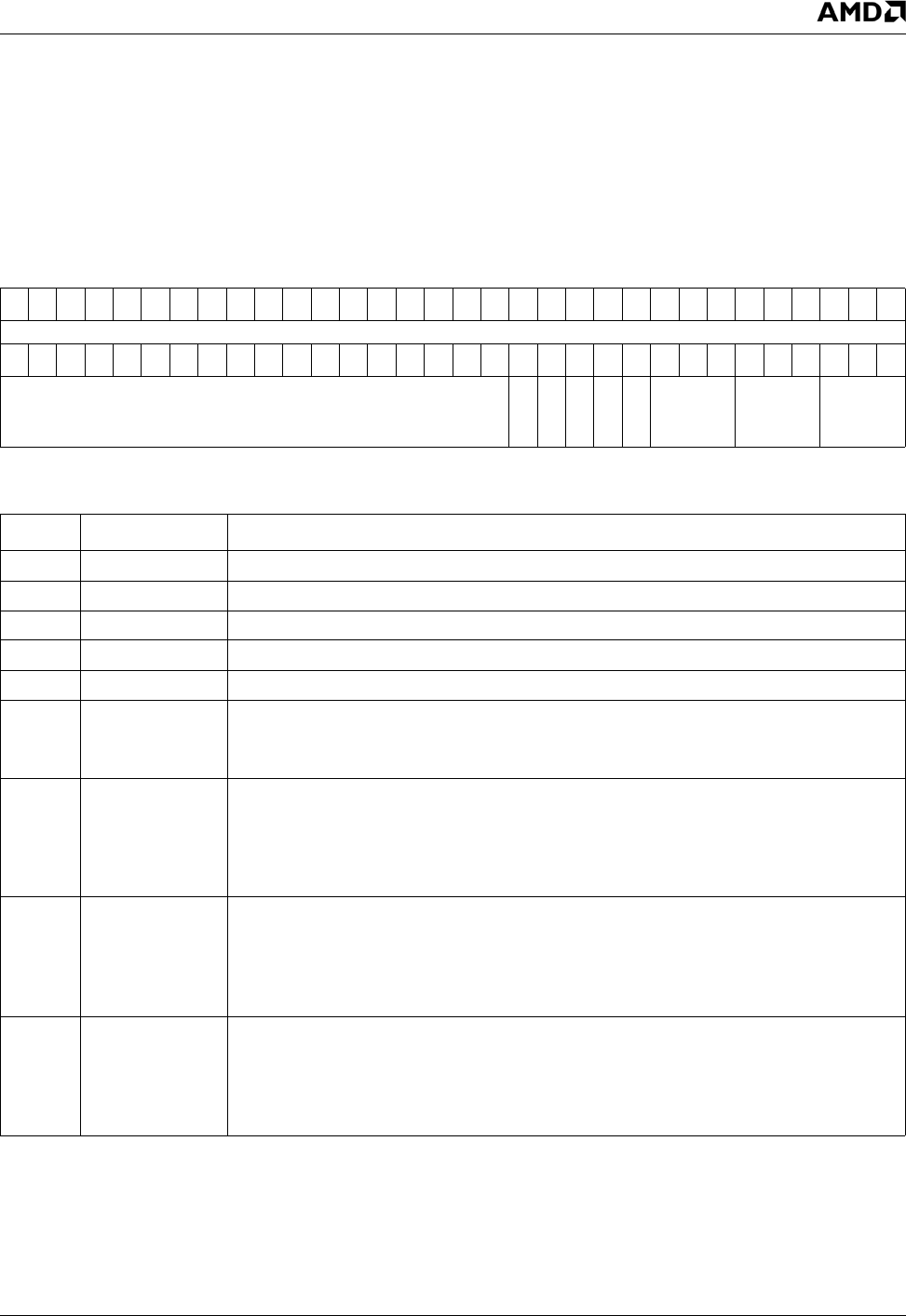

GLCP_DAC Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

SB

SG

SR

INREFEN

OL

AB AG AR

GLCP_DAC Bit Descriptions

Bit Name Description

64:14 RSVD Reserved.

13 SB (RO) Status Blue (Read only). A logic level 1 means the Blue DAC output is above 0.35V.

12 SG (RO) Status Green (Read only). A logic level 1 means the Green DAC output is above 0.35V.

11 SR (RO) Status Red (Read only). A logic level 1 means the Red DAC output is above 0.35V.

10 INREFEN Internal Reference Enable. Internal reference enable to the DAC.

9OL Output Level.

0: RGB.

1: TV - for testing only, analog TV out is not supported).

8:6 AB Adjust for Blue DAC.

000: 0%.

011: 7.5%.

100: -10%.

111: -2.5%.

5:3 AG Adjust for Green DAC.

000: 0%.

011: 7.5%.

100: -10%.

111: -2.5%.

2:0 AR Adjust for Red DAC.

000: 0%.

011: 7.5%.

100: -10%.

111: -2.5%.