370 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

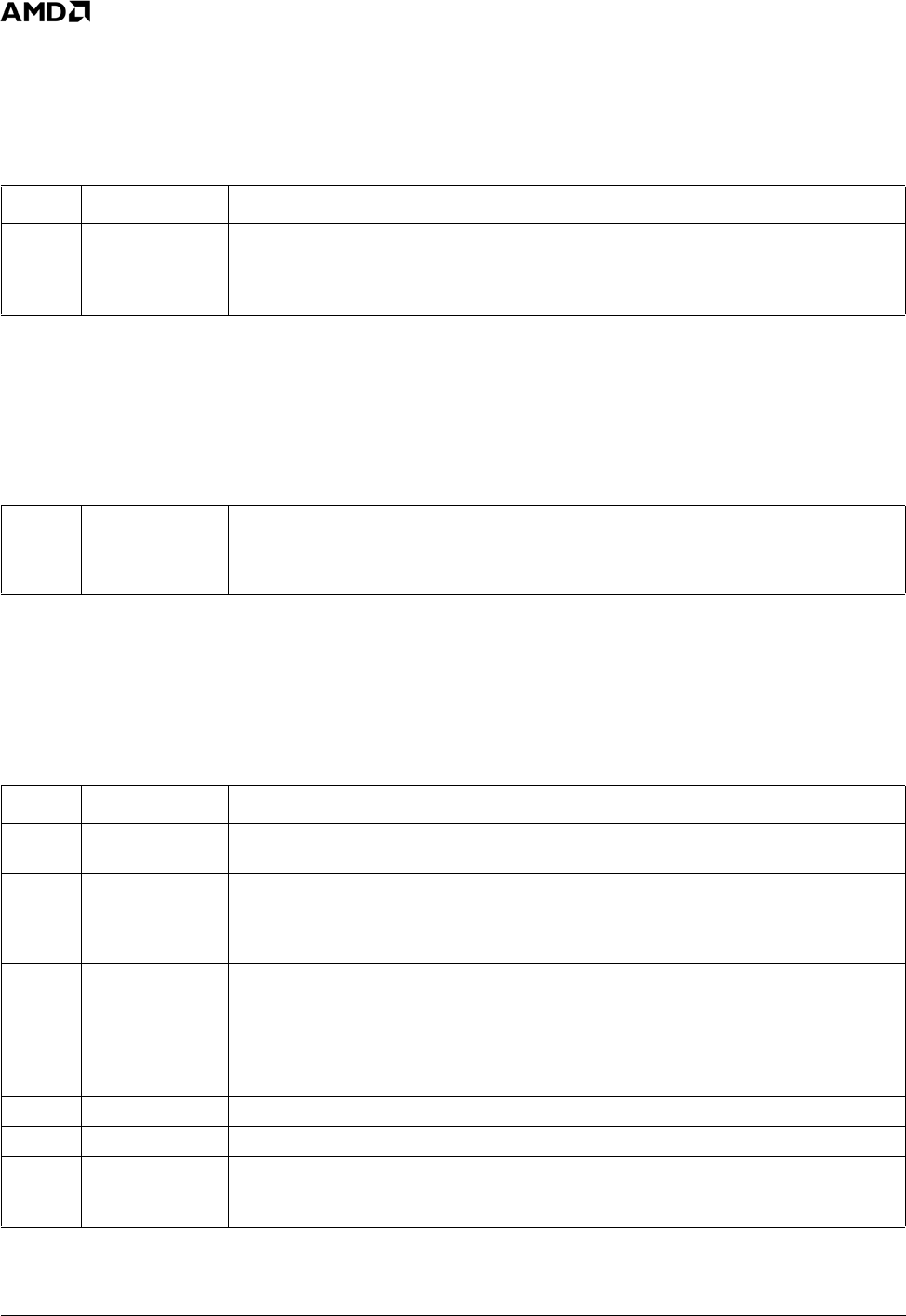

6.6.19.24 Vertical Blank Start

6.6.19.25 Vertical Blank End

6.6.19.26 CRTC Mode Control

Index 15h

Typ e R /W

Reset Value 00h

Vertical Blank Start Register Bit Descriptions

Bit Name Description

7:0 V_BL_ST Vertical Blank Start Register Bits [7:0]. This is the low eight bits of a value that speci-

fies the starting scan line of the vertical blank signal. This is a 10-bit value. Bit 8 is in the

Overflow register (Index 07h[3]) and bit 9 is in the Maximum Scan Line register (Index

09h[5]).

Index 16h

Typ e R /W

Reset Value 00h

Vertical Blank End Register Bit Descriptions

Bit Name Description

7:0 V_BL_END Vertical Blank End. This value specifies the low eight bits of a compare value that repre-

sents the scan line where the vertical blank signal goes inactive.

Index 17h

Typ e R /W

Reset Value 00h

CRTC Mode Control Register Bit Descriptions

Bit Name Description

7 ENSYNC Enable Syncs. When set to 1, this bit enables the horizontal and vertical sync signals.

When 0, this bit holds both sync flip-flops reset.

6BTMD Byte Mode. If the DWORD mode bit (DW, Index 14h[6]) is 0, then this bit configures the

CRTC addresses for byte addresses when set to 1, or WORD addresses when set to 0. If

DW is set to 1, then this bit is ignored. See Table 6-55 on page 371 for information on the

various CRTC addressing modes.

5AW Address Wrap. When the CRTC is addressing the frame buffer in Word Mode (Byte

Mode = 0, DWORD Mode = 0) then this bit determines which address bit occupies the

MA0 bit position of the address sent to the frame buffer memory. If Address Wrap = 0,

CRTC address counter bit 13 occupies the MA0 position. If Address Wrap = 1, then

CRTC address counter bit 15 is in the MA0 position. See Table 6-55 on page 371 for

information on the various CRTC addressing modes.

4 RSVD Reserved.

3 RSVD Not Implemented. (Count by 2)

2 VCKL_SL VCLK Select. This bit determines the clocking for the vertical portion of the CRTC. If this

bit is 0, the horizontal sync signal clocks the vertical section. If this bit is 1, the horizontal

sync divided by two clocks the vertical section.